We are attempting to write to PCIe (0x2000 0000 - 0x2FFF FFFF) from the 8168 DSP.

Here is what I have gleaned from various forum posts on the matter:

http://e2e.ti.com/support/dsp/davinci_digital_media_processors/f/717/p/130665/468712.aspx#468712

The masters on this device that can access PCIe registers directly are the Cortex-A8 and EDMA.

http://e2e.ti.com/support/dsp/davinci_digital_media_processors/f/716/p/127968/462261.aspx#462261

The only masters that can access the PCIe Registers are the ARM Cortex-A8 and the EDMA; the DSP can access it via the DEMMU only

http://e2e.ti.com/support/dsp/davinci_digital_media_processors/f/716/p/127968/484632.aspx#484632

The PCIe on this device is accessible by ARM and EDMA only. It is not feasible to access from the DSP.

The information above is conflicting; is it only possible to access the PCIe from the DSP via EDMA, or is it possible using DEMMU? Or must the two be used in conjunction?

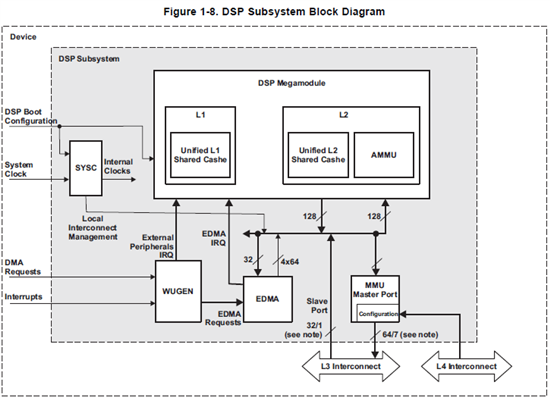

According to Figure 1-8 is the Tech Reference Manual (sprugx9), we should be able to access the L3 Interrconnect (including PCIe) from the DSP via the DEMMU:

Which of the following are valid options for writing to the PCIe memory area from the DSP? (The only thing that is clear from the above is the the DSP cannot directly access PCIe.)

- DSP --> EDMA --> PCIe

- DSP --> EDMA --> DEMMU --> PCIe

- DSP --> DEMMU --> PCIe