Other Parts Discussed in Thread: TMS320C6678

Hi experts,

During the I2C booting of the DSP (TMS320C6678), we figure out sometime the DSP will lock the I2C lines and then fail to boot but also lock the I2C EEPROM. The only way to solve the problem is to follow the TI Silicon errata I2C reset workaround(Errata usage note 6).

Please find more information here about our design and issue met:

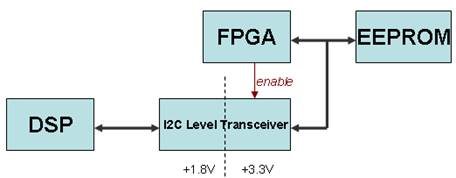

The I2C EEPROM is into a +3.3V environment. There is two I2C masters: First is an FPGA (direct connection), and second is an I2C Level Transceiver +1.8/+3.3V (PCA9306DCTT) connect to DSP. The transceiver enable pin is controlled by FPGA. FPGA is fully under our control.

During boot-up sequence (but also before and after), we verified and we are sure that the FPGA drive nothing (Keep Hi-Z) and transceiver is enabled and do not toggle.

To reproduce the error case, we just need to power cycle the DSP again and again (power of DSP is independent controlled by FPGA, it would not affect power of EEPROM.) until the DSP lock its I2C Reading. This error case is not easily reproducible. FPGA I2C interface and DSP power control interface are independent.

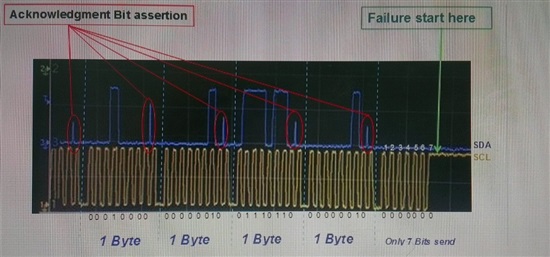

If we power on again the DSP, after error happened, no I2C command is sent by the DSP and SDA remain low.

The only way to “free” the bus is to generate an I2C command with FPGA. Basically, an I2C reading command sent by FPGA will make the EEPROM answer an error on the “acknowledgment” bit of the first sending byte, and then, will free the bus. A power cycle of the DSP after this point will make the I2C boot success.

For the Reset timing Sequence, We just follow the DSP Reset time diagram of the EVM board.

So far, we never got I2C reading/Writing error with FPGA command which exclude any EEPROM Issue.

After testing and review, we got then the certitude that the error come from the DSP side, and no others. Please help us to support on the issue.

Thanks in advance.