Hello,everyone

Recently,I learnt something about the register setting of AIC33. But I met a problem. I find a file named psp_aic33Codec.c file,which located in C:\dvsdk_1_11_00_00\pspdrivers_1_10_00\packages\ti\sdo\pspdrivers\system\dm6437\bios\evmDM6437\audio\src. some configuration is as follow(line 247 -261):

case 44100: /* FS = Fref/1 */

PLLB_Value = 0x20; // 0x20

PLLC_Value = 0x00; // 0x00

PLLD_Value = 0x00; // 0x00

fsRef = FSREF_44100;

sampleRateDiv = 0x00;

break;

case 8000: /* FS = Fref/6 */

PLLB_Value = 0x20;

PLLC_Value = 0x6E;

PLLD_Value = 0x23;

fsRef = FSREF_48000;

sampleRateDiv = 0x0A;

break;

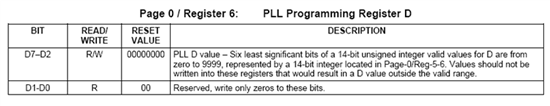

I have seen the tlv320aic33.pdf (http://www.ti.com.cn/cn/lit/ds/symlink/tlv320aic33.pdf)file. In page 46, the table as follow,it tells us that PLLValue should set to xxxxxx00.

However,I find the setting as follow:(IN psp_aic33Codec.c file)

case 8000: /* FS = Fref/6 */

PLLB_Value = 0x20;

PLLC_Value = 0x6E;

PLLD_Value = 0x23;

fsRef = FSREF_48000;

sampleRateDiv = 0x0A;

break;

The PLLD_Value is 0x23, which contradict with the tlv320aic33.pdf (http://www.ti.com.cn/cn/lit/ds/symlink/tlv320aic33.pdf)file .

So why this happens?

Following the tlv320aic33.pdf description,I can not calculate the PLLD = 0x23. How to calculate?

Thank you in advance. I am looking forward to your reply.

Zhao