Other Parts Discussed in Thread: TLV320AIC3120

Hi,

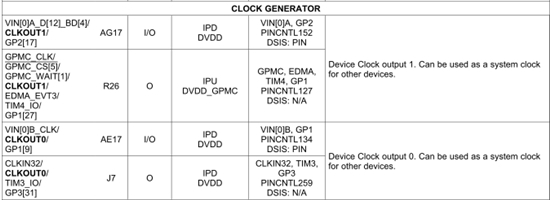

The DM8148 Clock Generator Terminal Functions have 4 pin of 2 port.

Q1. If the use pin AG17 for VIN[0]A and AE17 for VIN[0]B,the pin R26 and pin J7 can set output to driver other devices?

Q2. if use pin R26 or pin J7 to driver tlv320aic3120 MCLK ,how to set the clock frequency to 12.288MHz?

Q3. If not use pin R26 or pin J7,How can set the McASP0 Port pin MCA[0]_ACLKX out clock frequency to 1.536MHz?