Hi All,

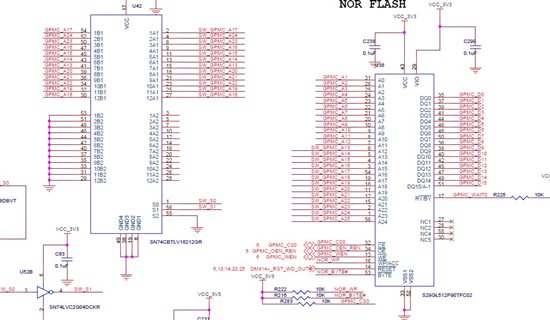

I have seen that (J28,K27,....) pins have been used for GPMC_A[1:12] signals on Mistral DM8148 board. This means designer has selected M1 option according to Table 4-2 on SPRS647D (page 153/54)

So I expected that M1 option pins should be used for GPMC_A[20:23] signals.(Please see PINCNTL113...116) But M0 options have been used for GPMC_A[20:23] signal on Mistral DM8148 board. I do not have a Mistral DM8148 board to test but I am sure any one has tested that if NOR Flash working properly for XIP boot.

Is there a simple point that I can not able to see or is there a confiliction between Table 4-2 on SPRS647D and Mistral DM8148 board schematics?

GPMC_A[20] (M0) AD28

GPMC_A[21] (M0) AC28

GPMC_A[22] (M0) AB27

GPMC_A[23] (M0) AA26

GPMC_A[24]/GPMC_A[20] L25

GPMC_A[25]/GPMC_A[21] N23

GPMC_A[26]/GPMC_A[22] P22

GPMC_A[27]/GPMC_A[23] R24

Best regards.