Hello,

6406.201210020942.pdfI'm using TI8167 , udworks DVRRDK03.00.00.00

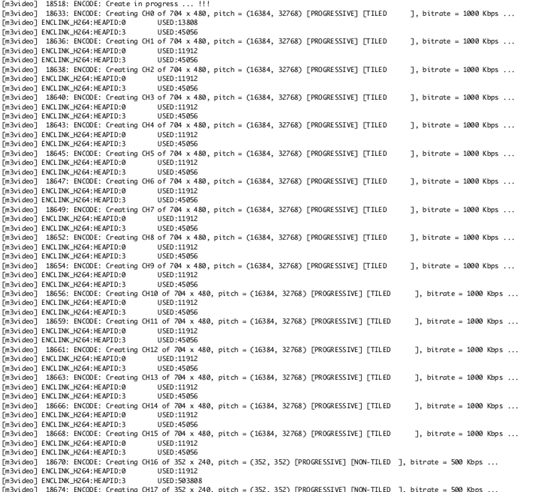

I think this error caused by asynchronous CVBS input. How can I solve this problem?

can i detour this problem by m3vpss reset?

[m3vpss ] AVSYNC:WallTime IGNORE Unexpected Discontinuity.PrevTs[9391770]/CurTs[9394072]

[m3vpss ] AVSYNC:WallTime IGNORE Unexpected Discontinuity.PrevTs[9394322]/CurTs[9396658]

[m3vpss ] AVSYNC:WallTime IGNORE Unexpected Discontinuity.PrevTs[9397008]/CurTs[9399294]

[m3vpss ] AVSYNC:WallTime IGNORE Unexpected Discontinuity.PrevTs[9399511]/CurTs[9400352]

[m3vpss ] AVSYNC:WallTime IGNORE Unexpected Discontinuity.PrevTs[9400352]/CurTs[9402080]

[m3vpss ] AVSYNC:WallTime IGNORE Unexpected Discontinuity.PrevTs[9402131]/CurTs[9402281]

[m3vpss ] AVSYNC:WallTime IGNORE Unexpected Discontinuity.PrevTs[9402281]/CurTs[9403041]