Hi Sir,

I have a question about 8148 DDR3 controller, I want to use only one DDR3 controller ,how to do with the other controller?

from spec page 286,

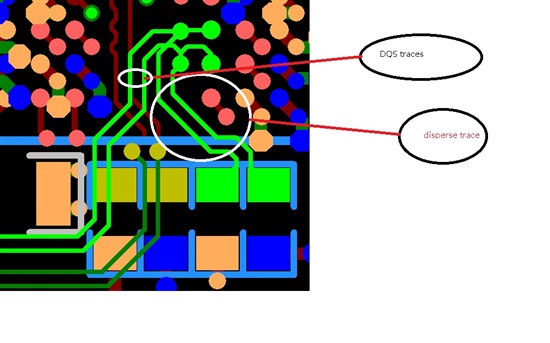

Note that the 16-bit wide interface schematic is practically identical to the 32-bit interface (see Figure 8-54

and Figure 8-55); only the high-word DDR memories are removed and the unused DQS inputs are tied off.

The processor DDR[x]_DQS[2] and DDR[x]_DQS[3] pins should be pulled to the DDR supply via 1-kΩ

resistors. Similarly, the DDR[x]_DQS[2] and DDR[x]_DQS[3] pins should be pulled to ground via 1-kΩ

resistors.

When not using a DDR interface, the proper method of handling the unused pins is to tie off the

DDR[x]_DQS[n] pins to the corresponding DVDD_DDR[x] supply via a 1-kΩ resistor and pulling the

DDR[x]_DQS[n] pins to ground via a 1k-Ω resistor. This needs to be done for each byte not used.

Although these signals have internal pullups and pulldowns, external pullups and pulldowns provide

additional protection against external electrical noise causing activity on the signals.

just add pull up/down resistors to DQS pins is enough?