Other Parts Discussed in Thread: DAC8555

Hello

I use a C6748 Device and need to service a DAC8555 over SPI0 with the EDMA3. Because of the 24Bit Word of the DAC8555 I split the 24Bit into three 8 Bit transfers. For this to work one need to hold the CSn for the duration of all three transfers. Between the last transfer and the first transfer for the next channel (next 24Bits) the DAC8555 needs a delay. Therefore I have tried the following with the EDMA:

1. Write 0x10 to the highest byte in SPIDAT1

2. Write the first data byte to the lowest byte in SPIDAT1 (initiate the first transfer)

3. Write 0x10 to the highest byte in SPIDAT1

4. Write the second data byte to the lowest byte in SPIDAT1 (initiate the 2nd transfer)

5. Write 0x04 to the highest byte in SPIDAT1 (use WDELAY)

6. Write the 3rd data byte to the lowest byte in SPIDAT1 (initiate the 3rd transfer)

The result : SPI transfer did not work as expected.

Then I have tried the following:

1. Write 0x14 to the highest byte in SPIDAT1

2. Write the first data byte to the lowest byte in SPIDAT1 (initiate the first transfer)

3. Write 0x14 to the highest byte in SPIDAT1

4. Write the second data byte to the lowest byte in SPIDAT1 (initiate the 2nd transfer)

5. Write 0x04 to the highest byte in SPIDAT1 (use WDELAY)

6. Write the 3rd data byte to the lowest byte in SPIDAT1 (initiate the 3rd transfer)

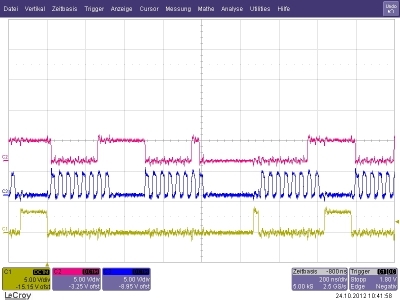

Result: SPI transfer most of the time looks ok. But sometimes the CSn does not work as expected (please see picture)

C1: CSn

C2: SCLK

C3: Data

The manual (spruh79A, chapter 28) does not tell any problems or notes about that behaviour. If I write 32Bit to SPIDAT1 the result is ok. But with EDMA3 only byte writes are possible (?).

Is there any easy solution to this problem? Any known Silicon problems?

Thanks.

Best regards,

Patrick