Dear TI

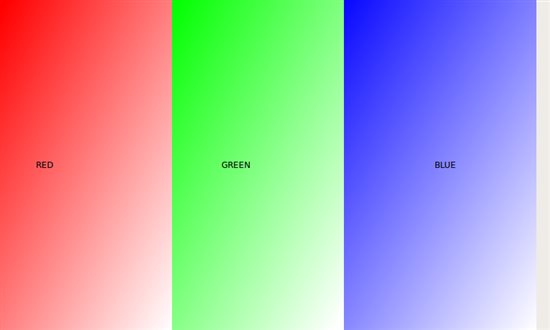

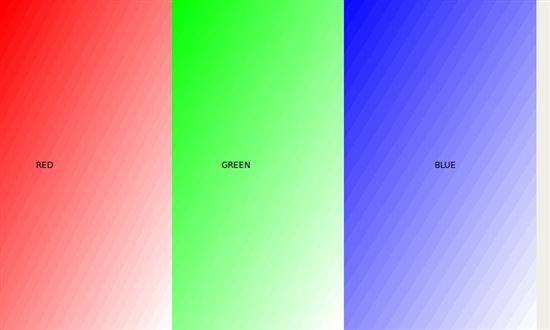

We are using DM 368 processor and a 24 bit PRGB interfaced LCD (from Truly ) having resolution of 800 * 480 ( size is 7 ''). We have an application which shows gradient of colors in Red, Green, Blue. This application was compiled for the PC and DM368. When we execute on PC Gradient looks very smooth there is no blocking effect (see PC_Image.BMP) but when we execute application for the DM368 we are getting blocking effect (see DM368_Image.BMP). It looks like it is showing application output in 16 bit colors.

We recompiled QT with 24 bit configuration only even then we are getting same result.

How to achieve 24 bit images of QT on LCD output of DM368.

Image Quality seen on PC

Image Quality When displayed on DM 368

Regards

pradeep