Other Parts Discussed in Thread: DM3730

Hi!

I'm using DM3730 with FPGA (connected via GPMC).

My DMA setup:

p347_fpga_info.dma_par.data_type = OMAP_DMA_DATA_TYPE_S16;

p347_fpga_info.dma_par.src_start = fpga_mem_read_base;

p347_fpga_info.dma_par.src_amode = OMAP_DMA_AMODE_POST_INC;

p347_fpga_info.dma_par.dst_start = p347_fpga_info.dma_rd_addr;

p347_fpga_info.dma_par.dst_amode = OMAP_DMA_AMODE_POST_INC;

p347_fpga_info.dma_par.dst_ei = 1;

p347_fpga_info.dma_par.dst_fi = 1;

p347_fpga_info.dma_par.elem_count = 8*64;

p347_fpga_info.dma_par.frame_count = 1;

p347_fpga_info.dma_par.sync_mode = OMAP_DMA_SYNC_FRAME;

ret = omap_request_dma(77,"p347_fpga_read_dma",p347_fpga_dma_callback,&p347_fpga_info,&p347_fpga_info.dma_ch);

omap_set_dma_params(p347_fpga_info.dma_ch,&p347_fpga_info.dma_par);

omap_set_dma_src_burst_mode(p347_fpga_info.dma_ch,OMAP_DMA_DATA_BURST_8);

omap_set_dma_dest_burst_mode(p347_fpga_info.dma_ch,OMAP_DMA_DATA_BURST_8);

My GPMC timings:

cswrofftime = 5

csrdofftime = 23

csextradelay = 0

csontime = 0

advwrofftime = 2

advrdofftime = 4

advextradelay = 0

advontime = 1

weofftime = 5

weextradelay = 0

weontime = 3

oeofftime = 22

oeextradelay = 0

oeontime = 6

pageburstaccesstime = 2

rdaccesstime = 7

wrcycletime = 7

rdcycletime = 8

wraccesstime = 3

wrdataonadmuxbus = 2

cycle2cycledelay = 1

cycle2cyclesamecsen = 0

cycle2cyclediffcsen = 1

busturnaround = 1

And my problem:

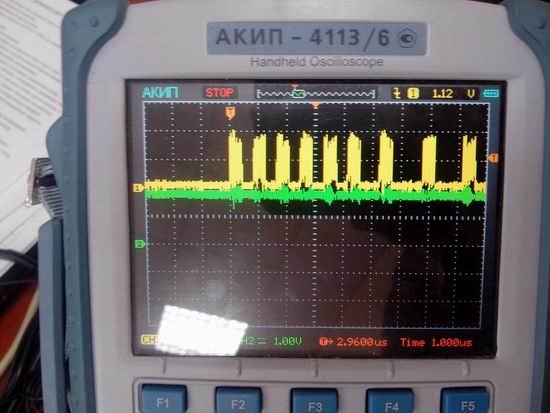

When DM3730 reads data from FPGA, an unpredictable delay between bursts appears.

Please look at photo: why delays are so large? Why they are different? Every burst is correct.

Yellow line is GPMC_CLK.