We are trying to get the SRIO bus to work between a TMS320C6678 DSP and an FPGA on the same circuit board. The aim is to run each of the four ports at 3.125 Gbps. We have modified the SRIOLoopbackDioIsr example from pdk_C6678_1_0_0_15 slightly:

/* Configure SRIO ports to operate in loopback mode. */

// CSL_SRIO_SetLoopbackMode(hSrio, 0);

// CSL_SRIO_SetLoopbackMode(hSrio, 1);

// CSL_SRIO_SetLoopbackMode(hSrio, 2);

// CSL_SRIO_SetLoopbackMode(hSrio, 3);

CSL_SRIO_SetNormalMode(hSrio, 0);

CSL_SRIO_SetNormalMode(hSrio, 1);

CSL_SRIO_SetNormalMode(hSrio, 2);

CSL_SRIO_SetNormalMode(hSrio, 3);

/* Assuming the link rate is 3125; program the PLL accordingly. */

CSL_BootCfgSetSRIOSERDESConfigPLL (0x229); // 5x, 156.25 MHz clock

// CSL_BootCfgSetSRIOSERDESConfigPLL (0x251); // 10x

// CSL_BootCfgSetSRIOSERDESConfigPLL (0x281); // 16x

CSL_BootCfgSetSRIOSERDESRxConfig (0, 0x00440485); // No loopback, full rate

CSL_BootCfgSetSRIOSERDESRxConfig (1, 0x00440485);

CSL_BootCfgSetSRIOSERDESRxConfig (2, 0x00440485);

CSL_BootCfgSetSRIOSERDESRxConfig (3, 0x00440485);

// CSL_BootCfgSetSRIOSERDESRxConfig (0, 0x00440495); // No loopback, half rate

// CSL_BootCfgSetSRIOSERDESRxConfig (1, 0x00440495);

// CSL_BootCfgSetSRIOSERDESRxConfig (2, 0x00440495);

// CSL_BootCfgSetSRIOSERDESRxConfig (3, 0x00440495);

CSL_BootCfgSetSRIOSERDESTxConfig (0, 0x00180785); // No loopback, full rate

CSL_BootCfgSetSRIOSERDESTxConfig (1, 0x00180785);

CSL_BootCfgSetSRIOSERDESTxConfig (2, 0x00180785);

CSL_BootCfgSetSRIOSERDESTxConfig (3, 0x00180785);

// CSL_BootCfgSetSRIOSERDESTxConfig (0, 0x00180795); // No loopback, half rate

// CSL_BootCfgSetSRIOSERDESTxConfig (1, 0x00180795);

// CSL_BootCfgSetSRIOSERDESTxConfig (2, 0x00180795);

// CSL_BootCfgSetSRIOSERDESTxConfig (3, 0x00180795);

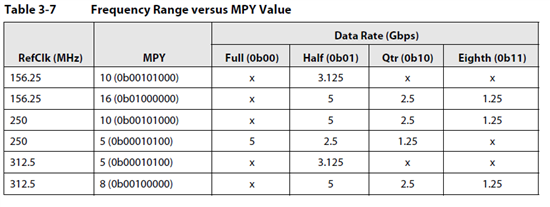

The above configuration with MPY 5 and full rate gives the desired 3.125 Gbps and the PLL is locked all the time, but when we try to change to MPY 10 and half rate (also gives 3.125 Gbps), the PLL is locked most of the time, but sometimes it gets unlocked. With MPY values at 8 or below the PLL is always locked, but above 8 the PLL gets unstable. We have checked the 156.25 MHz clock and has very low jitter.

Has anyone had similar PLL problems?