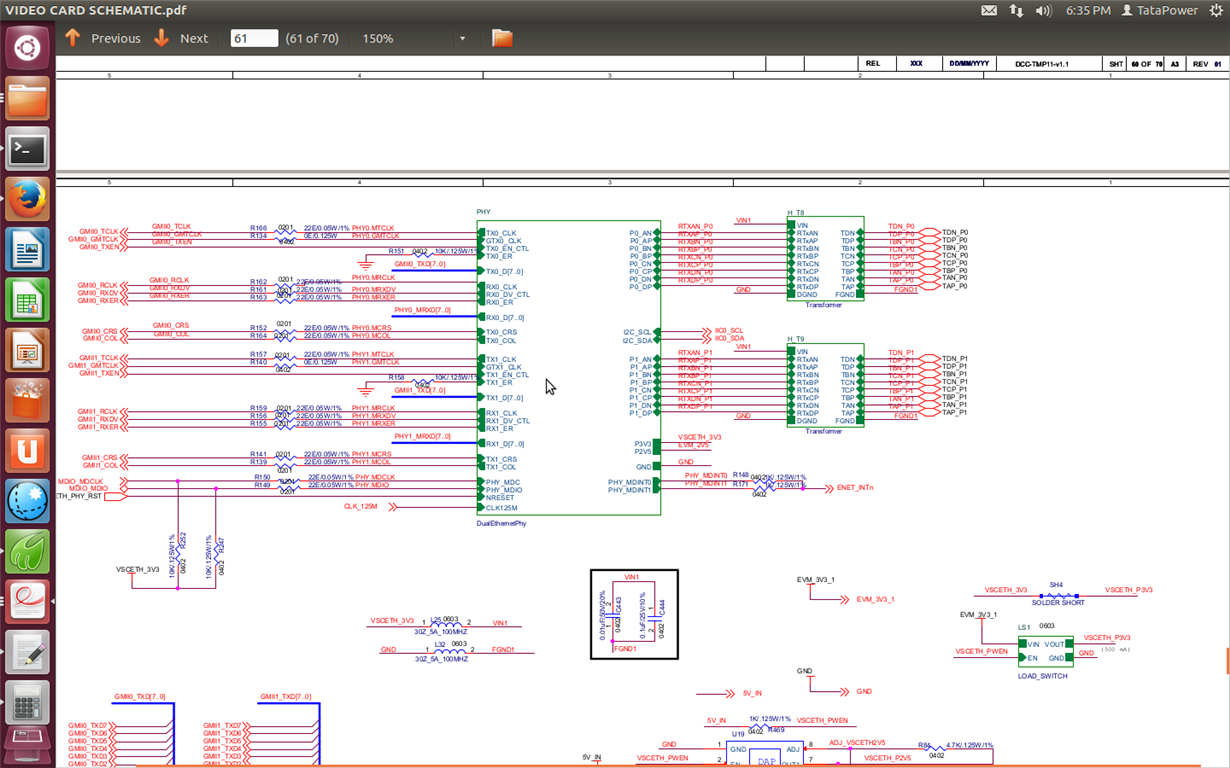

We built a custom DM8168-based module with a Lantiq gigabit ethernet PHY. Unfortunatelly, too late we realised that DM8168 has specific needs regarding gigabit ethernet operation - clock to DM's EMAC_TXCLK must be provided even in gigabit mode (according to DM's silicon errata, Advisory 2.1.18), which is not a common option in PHYs since GMII mode officially doesn't require this. ET1011C on the EVM provides this as an option (PHY Configuration Register, bit "Transmit Clock Enable"), but it's not standard feature.

Can someone recommend a PHY which is known to work in gigabit mode with DM8168 (or Sitara AM3894 or Integra C6A8168)? That is, a PHY which can output 125 MHz to TX_CLK in GMII mode. Of course, beside ET1011C which is used on the EVM and it's hard to find now.

Thanks in advance!