I'm using PSP 1_10_03 with DM6437 and want to read data from SPI Flash (ST microelectronics M25P32).

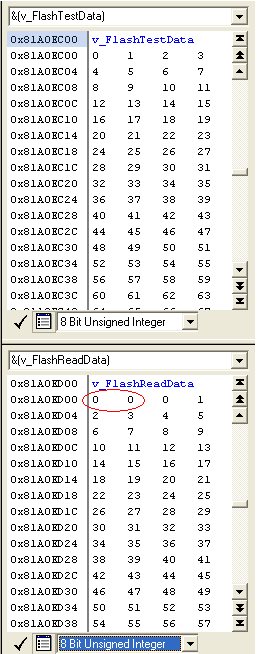

First a SPI flash sector is erased and a new set of data is written into it, but when a data is Read back from that Sector it is inconsistent to the data written to the SPI FLash. It looks like the first two bytes are incorrect and after that all the data comes properly.

#include <ti/sdo/pspdrivers/soc/dm6437/dsp/csl_types.h>

#include <ti/sdo/pspdrivers/soc/dm6437/dsp/soc.h>

#include <ti/sdo/pspdrivers/soc/dm6437/dsp/cslr_uart.h>

#include <ti/sdo/pspdrivers/soc/dm6437/dsp/cslr_psc.h>

#include <ti/sdo/pspdrivers/soc/dm6437/dsp/cslr_sys.h>

#include <ti/sdo/pspdrivers/soc/dm6437/dsp/cslr_mcbsp.h>

#include <ti/sdo/pspdrivers/soc/dm6437/dsp/cslr_gpio.h>

uint32_t Flash_SectorErase(uint32_t SectorAddress){

uint32_t statusReg;

uint32_t tmpGpioReg;

CSL_McbspRegsOvly mcbspRegs = (CSL_McbspRegsOvly)CSL_MCBSP_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

CSL_GpioRegsOvly gpioRegs = (CSL_GpioRegsOvly)CSL_GPIO_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

/*------------------------------------------------------------- */

/* Issue Write enable Command */

/*------------------------------------------------------------- */

Flash_write_command(SPI_WREN_COMMAND);

/*------------------------------------------------------------- */

/* Global Unprotect sectors. */

/*------------------------------------------------------------- */

tmpGpioReg = DRIVE_CS_LOW (gpioRegs);

while((tmpGpioReg & GPIO97_MASK) != 0u){

}

/* Send WSR (write status reg) opcode to read status register */

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((SPI_WSR_COMMAND >> 24u) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = 0u;

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

tmpGpioReg = DRIVE_CS_HIGH (gpioRegs);

while(!(tmpGpioReg & GPIO97_MASK)){

}

/* Wait while device is busy.. */

do {

statusReg = Flash_read_status_reg();

} while( (statusReg & 0x1u) != 0u );

/* =============================================================

* Sada: Any command executed, disables the write enable bit !!!

* Set the bit again before any-thing else.

* ============================================================= */

do {

Flash_write_command(SPI_WREN_COMMAND);

/* ---------------------------------------------------------- */

/* Read status reg and ensure device is write enabled. */

/* ---------------------------------------------------------- */

statusReg = Flash_read_status_reg();

} while( (statusReg & 0xFu) != 2u);

waitloop(60u);

/* ---------------------------------------------------------- */

/* Read status reg and ensure device is write enabled. */

/* ---------------------------------------------------------- */

tmpGpioReg = DRIVE_CS_LOW (gpioRegs);

while((tmpGpioReg & GPIO97_MASK) != 0u){

}

/* Send WSR (write status reg) opcode to read status register */

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((0x000000D8u ) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((SectorAddress >> 16u ) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((SectorAddress >> 8u ) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((SectorAddress >> 0u) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

waitloop(100u);

tmpGpioReg = DRIVE_CS_HIGH (gpioRegs);

while(!(tmpGpioReg & GPIO97_MASK)){

}

/* Needed some delay */

waitloop(1000u);

/* Wait while device is busy.. */

do {

statusReg = Flash_read_status_reg();

} while( (statusReg & 0x1u) != 0u );

return 0u;

}

uint32_t Flash_read_status_reg(void){

uint32_t statusReg;

uint32_t tmpGpioReg;

CSL_McbspRegsOvly mcbspRegs = (CSL_McbspRegsOvly)CSL_MCBSP_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

CSL_GpioRegsOvly gpioRegs = (CSL_GpioRegsOvly)CSL_GPIO_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

tmpGpioReg = DRIVE_CS_LOW (gpioRegs);

while((tmpGpioReg & GPIO97_MASK) != 0u){

}

/* Send WRSR opcode to read status register */

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((SPI_RSR_COMMAND >> 24u) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = 0u;

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

statusReg = (uint32_t)(mcbspRegs->DRR);

waitloop(0x20u);

tmpGpioReg = DRIVE_CS_HIGH (gpioRegs);

while(!(tmpGpioReg & GPIO97_MASK)){

}

return statusReg;

}

void Flash_write_command(uint32_t cmd){

uint32_t tmpGpioReg;

CSL_McbspRegsOvly mcbspRegs = (CSL_McbspRegsOvly)CSL_MCBSP_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

CSL_GpioRegsOvly gpioRegs = (CSL_GpioRegsOvly)CSL_GPIO_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

/*------------------------------------------------------------- */

/* Issue Write enable Command */

/*------------------------------------------------------------- */

tmpGpioReg = DRIVE_CS_LOW (gpioRegs);

while((tmpGpioReg & GPIO97_MASK) != 0u){

}

waitloop(0x20u);

/* Poll for XRDY flag to acknowledge transmitter is ready */

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)(cmd >>24u);

waitloop(0x20u);

tmpGpioReg = DRIVE_CS_HIGH (gpioRegs);

while(!(tmpGpioReg & GPIO97_MASK)){

}

}

void Flash_ReadBytes(uint32_t eeprom_addr, sint32_t num_bytes, uint8_t dest_buff[]){

uint32_t byte32;

sint32_t i;

uint32_t tmpGpioReg;

CSL_McbspRegsOvly mcbspRegs = (CSL_McbspRegsOvly)CSL_MCBSP_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

CSL_GpioRegsOvly gpioRegs = (CSL_GpioRegsOvly)CSL_GPIO_0_REGS; /*PRQA S 303 */ /* cast for CSL register */

uint32_t read_cmd = 0x03000000u;

/*-------------------------------------------------------------- */

tmpGpioReg = DRIVE_CS_LOW (gpioRegs);

while((tmpGpioReg & GPIO97_MASK) != 0u){

}

waitloop(0x20u);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)(((read_cmd | eeprom_addr)>>24u) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

byte32 = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((eeprom_addr>>16u) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

byte32 = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)((eeprom_addr>>8u) & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

byte32 = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = (uint32_t)(eeprom_addr & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

byte32 = (uint32_t)(mcbspRegs->DRR);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = 0u;

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

byte32 = (uint32_t)(mcbspRegs->DRR);

waitloop(0x20u);

for(i = 0; i < num_bytes; i++){

dest_buff[i] = (uint8_t)(byte32 & 0xFFu);

for (;;) {

if (CSL_MCBSP_SPCR_XRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_XRDY)) {

break;

}

}

mcbspRegs->DXR = 0u;

for (;;) {

if (CSL_MCBSP_SPCR_RRDY_YES == CSL_FEXT(mcbspRegs->SPCR,MCBSP_SPCR_RRDY)) {

break;

}

}

byte32 = (uint32_t)(mcbspRegs->DRR);

waitloop(0x20u);

}

tmpGpioReg = DRIVE_CS_HIGH (gpioRegs);

while(!(tmpGpioReg & GPIO97_MASK)){

}

}