Hello,

I don't feel like an expert on caching so this may be some simple questions.

1. I was wondering, when and why I should use BIOS cache and if there is an example?

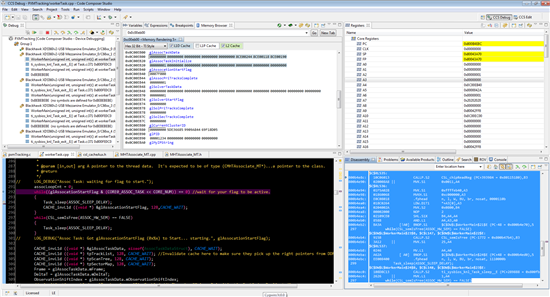

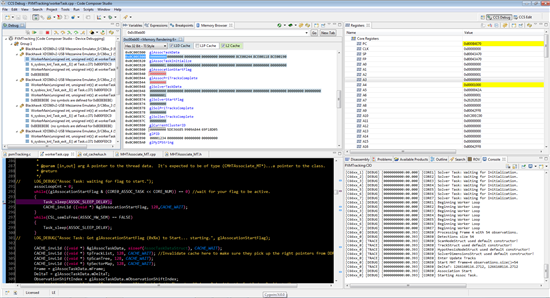

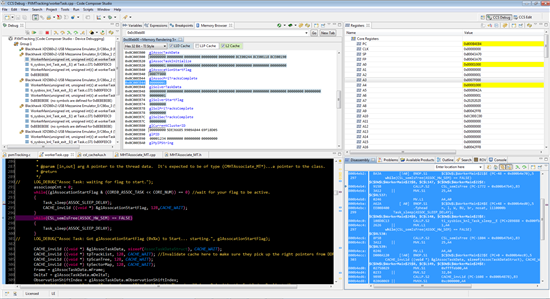

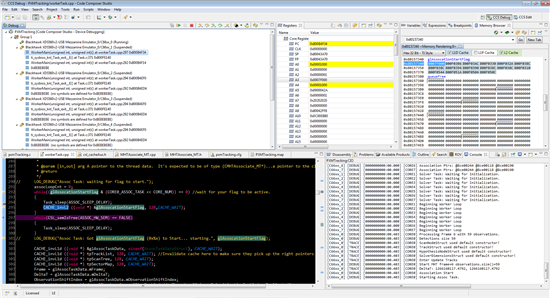

2. I am using CSL caching. When I ask it to invalid just the size of the variable, I get undefined behavoir. Sometimes it works but if I readjust the memory map, then it might not.

CACHE_invL1d((void *) &glAssocationStartFlag, sizeof(unsigned int), CACHE_WAIT);

All the examples use 128, so I thought that value must just have been chosen as the default. But I am thinking now, maybe not. Why do they use 128?

CACHE_invL1d((void *) &glAssocationStartFlag, 128, CACHE_WAIT);

3. What if I want to invalidate a variable (such as a struct) that is larger than 128, what should i do?

Thanks,

brandy