Hi,

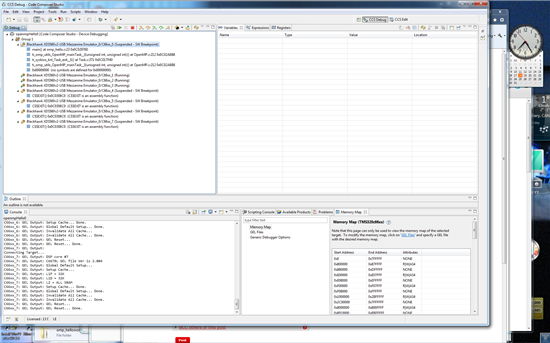

I try to run the simple openmp hello world example. After launching the project to emulator 560v2 in the EVM6678, it is in a running status, see below figure:

The core0 stops while core 1, 2 and 3 are running, core 4,5,6 and 7 seem no loading code. This does not look like the normal launching case. Of course, there is no correct echo message in the console window.

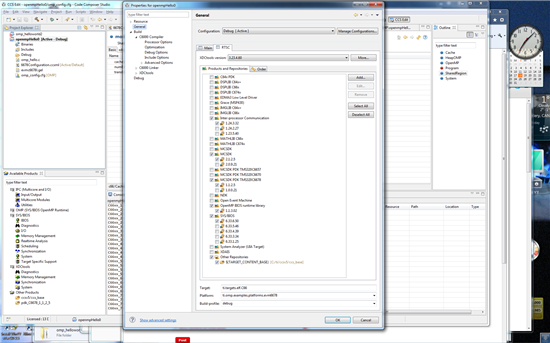

The tools used are shown as:

I have no idea what tool may be outdated or not.

This is the echo message when launching:

C66xx_0: GEL Output: Setup_Memory_Map...

C66xx_0: GEL Output: Setup_Memory_Map... Done.

C66xx_1: GEL Output: Setup_Memory_Map...

C66xx_1: GEL Output: Setup_Memory_Map... Done.

C66xx_2: GEL Output: Setup_Memory_Map...

C66xx_2: GEL Output: Setup_Memory_Map... Done.

C66xx_3: GEL Output: Setup_Memory_Map...

C66xx_3: GEL Output: Setup_Memory_Map... Done.

C66xx_4: GEL Output: Setup_Memory_Map...

C66xx_4: GEL Output: Setup_Memory_Map... Done.

C66xx_5: GEL Output: Setup_Memory_Map...

C66xx_5: GEL Output: Setup_Memory_Map... Done.

C66xx_6: GEL Output: Setup_Memory_Map...

C66xx_6: GEL Output: Setup_Memory_Map... Done.

C66xx_7: GEL Output: Setup_Memory_Map...

C66xx_7: GEL Output: Setup_Memory_Map... Done.

C66xx_0: GEL Output:

Connecting Target...

C66xx_0: GEL Output: DSP core #0

C66xx_0: GEL Output: C6678L GEL file Ver is 2.004

C66xx_0: GEL Output: Global Default Setup...

C66xx_0: GEL Output: Setup Cache...

C66xx_0: GEL Output: L1P = 32K

C66xx_0: GEL Output: L1D = 32K

C66xx_0: GEL Output: L2 = ALL SRAM

C66xx_0: GEL Output: Setup Cache... Done.

C66xx_0: GEL Output: Main PLL (PLL1) Setup ...

C66xx_0: GEL Output: PLL1 Setup for DSP @ 1000.0 MHz.

C66xx_0: GEL Output: SYSCLK2 = 333.3333 MHz, SYSCLK5 = 200.0 MHz.

C66xx_0: GEL Output: SYSCLK8 = 15.625 MHz.

C66xx_0: GEL Output: PLL1 Setup... Done.

C66xx_0: GEL Output: Power on all PSC modules and DSP domains...

C66xx_0: GEL Output: Security Accelerator disabled!

C66xx_0: GEL Output: Power on all PSC modules and DSP domains... Done.

C66xx_0: GEL Output: PA PLL (PLL3) Setup ...

C66xx_0: GEL Output: PA PLL Setup... Done.

C66xx_0: GEL Output: DDR3 PLL (PLL2) Setup ...

C66xx_0: GEL Output: DDR3 PLL Setup... Done.

C66xx_0: GEL Output: DDR begin (1333 auto)

C66xx_0: GEL Output: XMC Setup ... Done

C66xx_0: GEL Output:

DDR3 initialization is complete.

C66xx_0: GEL Output: DDR done

C66xx_0: GEL Output: DDR3 memory test... Started

C66xx_0: GEL Output: DDR3 memory test... Passed

C66xx_0: GEL Output: PLL and DDR Initialization completed(0) ...

C66xx_0: GEL Output: configSGMIISerdes Setup... Begin

C66xx_0: GEL Output:

SGMII SERDES has been configured.

C66xx_0: GEL Output: Enabling EDC ...

C66xx_0: GEL Output: L1P error detection logic is enabled.

C66xx_0: GEL Output: L2 error detection/correction logic is enabled.

C66xx_0: GEL Output: MSMC error detection/correction logic is enabled.

C66xx_0: GEL Output: Enabling EDC ...Done

C66xx_0: GEL Output: Configuring CPSW ...

C66xx_0: GEL Output: Configuring CPSW ...Done

C66xx_0: GEL Output: Global Default Setup... Done.

C66xx_0: GEL Output: Invalidate All Cache...

C66xx_0: GEL Output: Invalidate All Cache... Done.

C66xx_0: GEL Output: GEL Reset...

C66xx_0: GEL Output: GEL Reset... Done.

C66xx_0: GEL Output: Disable all EDMA3 interrupts and events.

C66xx_1: GEL Output:

Connecting Target...

C66xx_1: GEL Output: DSP core #1

C66xx_1: GEL Output: C6678L GEL file Ver is 2.004

C66xx_1: GEL Output: Global Default Setup...

C66xx_1: GEL Output: Setup Cache...

C66xx_1: GEL Output: L1P = 32K

C66xx_1: GEL Output: L1D = 32K

C66xx_1: GEL Output: L2 = ALL SRAM

C66xx_1: GEL Output: Setup Cache... Done.

C66xx_1: GEL Output: Global Default Setup... Done.

C66xx_1: GEL Output: Invalidate All Cache...

C66xx_1: GEL Output: Invalidate All Cache... Done.

C66xx_1: GEL Output: GEL Reset...

C66xx_1: GEL Output: GEL Reset... Done.

C66xx_2: GEL Output:

Connecting Target...

C66xx_2: GEL Output: DSP core #2

C66xx_2: GEL Output: C6678L GEL file Ver is 2.004

C66xx_2: GEL Output: Global Default Setup...

C66xx_2: GEL Output: Setup Cache...

C66xx_2: GEL Output: L1P = 32K

C66xx_2: GEL Output: L1D = 32K

C66xx_2: GEL Output: L2 = ALL SRAM

C66xx_2: GEL Output: Setup Cache... Done.

C66xx_2: GEL Output: Global Default Setup... Done.

C66xx_2: GEL Output: Invalidate All Cache...

C66xx_2: GEL Output: Invalidate All Cache... Done.

C66xx_2: GEL Output: GEL Reset...

C66xx_2: GEL Output: GEL Reset... Done.

C66xx_3: GEL Output:

Connecting Target...

C66xx_3: GEL Output: DSP core #3

C66xx_3: GEL Output: C6678L GEL file Ver is 2.004

C66xx_3: GEL Output: Global Default Setup...

C66xx_3: GEL Output: Setup Cache...

C66xx_3: GEL Output: L1P = 32K

C66xx_3: GEL Output: L1D = 32K

C66xx_3: GEL Output: L2 = ALL SRAM

C66xx_3: GEL Output: Setup Cache... Done.

C66xx_3: GEL Output: Global Default Setup... Done.

C66xx_3: GEL Output: Invalidate All Cache...

C66xx_3: GEL Output: Invalidate All Cache... Done.

C66xx_3: GEL Output: GEL Reset...

C66xx_3: GEL Output: GEL Reset... Done.

C66xx_4: GEL Output:

Connecting Target...

C66xx_4: GEL Output: DSP core #4

C66xx_4: GEL Output: C6678L GEL file Ver is 2.004

C66xx_4: GEL Output: Global Default Setup...

C66xx_4: GEL Output: Setup Cache...

C66xx_4: GEL Output: L1P = 32K

C66xx_4: GEL Output: L1D = 32K

C66xx_4: GEL Output: L2 = ALL SRAM

C66xx_4: GEL Output: Setup Cache... Done.

C66xx_4: GEL Output: Global Default Setup... Done.

C66xx_4: GEL Output: Invalidate All Cache...

C66xx_4: GEL Output: Invalidate All Cache... Done.

C66xx_4: GEL Output: GEL Reset...

C66xx_4: GEL Output: GEL Reset... Done.

C66xx_5: GEL Output:

Connecting Target...

C66xx_5: GEL Output: DSP core #5

C66xx_5: GEL Output: C6678L GEL file Ver is 2.004

C66xx_5: GEL Output: Global Default Setup...

C66xx_5: GEL Output: Setup Cache...

C66xx_5: GEL Output: L1P = 32K

C66xx_5: GEL Output: L1D = 32K

C66xx_5: GEL Output: L2 = ALL SRAM

C66xx_5: GEL Output: Setup Cache... Done.

C66xx_5: GEL Output: Global Default Setup... Done.

C66xx_5: GEL Output: Invalidate All Cache...

C66xx_5: GEL Output: Invalidate All Cache... Done.

C66xx_5: GEL Output: GEL Reset...

C66xx_5: GEL Output: GEL Reset... Done.

C66xx_6: GEL Output:

Connecting Target...

C66xx_6: GEL Output: DSP core #6

C66xx_6: GEL Output: C6678L GEL file Ver is 2.004

C66xx_6: GEL Output: Global Default Setup...

C66xx_6: GEL Output: Setup Cache...

C66xx_6: GEL Output: L1P = 32K

C66xx_6: GEL Output: L1D = 32K

C66xx_6: GEL Output: L2 = ALL SRAM

C66xx_6: GEL Output: Setup Cache... Done.

C66xx_6: GEL Output: Global Default Setup... Done.

C66xx_6: GEL Output: Invalidate All Cache...

C66xx_6: GEL Output: Invalidate All Cache... Done.

C66xx_6: GEL Output: GEL Reset...

C66xx_6: GEL Output: GEL Reset... Done.

C66xx_7: GEL Output:

Connecting Target...

C66xx_7: GEL Output: DSP core #7

C66xx_7: GEL Output: C6678L GEL file Ver is 2.004

C66xx_7: GEL Output: Global Default Setup...

C66xx_7: GEL Output: Setup Cache...

C66xx_7: GEL Output: L1P = 32K

C66xx_7: GEL Output: L1D = 32K

C66xx_7: GEL Output: L2 = ALL SRAM

C66xx_7: GEL Output: Setup Cache... Done.

C66xx_7: GEL Output: Global Default Setup... Done.

C66xx_7: GEL Output: Invalidate All Cache...

C66xx_7: GEL Output: Invalidate All Cache... Done.

C66xx_7: GEL Output: GEL Reset...

C66xx_7: GEL Output: GEL Reset... Done.

They are righ?

I have used the GEL as the link said:

http://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/t/199072.aspx

I check the .cfg file and do not see the setting to run the core number (4 loading code above) yet. I do see there are 4 threads in the main().

I do not add a link cmd file yet. If it needs, which one I can use?

Thanks,