hi,

I'm fighting with PCIe boot from another DSP EVM board via custom backplane.

I have two C6657EVM boards and a custom AMC backplace which completed PCIe communication between RC and EP using the sample soft as below.

C:\ti\pdk_C6657_1_1_2_5\packages\ti\drv\exampleProjects\PCIE_exampleProject

I figured that one C6657EVM(EP side) with PCIe boots from another C6657EVM board(RC side) via custom AMC backplace.

But I can not pass the LINK TRAINING.

I find LOCK bit of register PCIE_SERDES_STS in EP side is still 0 after powered on.

Is there any issues on this C6657evm board?

PS:

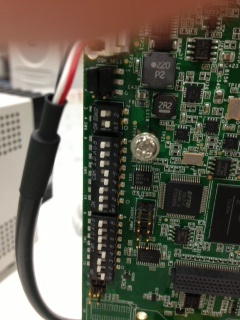

I updated the latest IBL on the C6657 board of the EP side and set dipswitches as below.

LENDIAN=1 System is operating in Little Endian mode

BOOT[3:0]=0100 (PCIe boot)

BOOT4 Reserved =>0

BOOT[8:5]=0000 32bit

BOOT[9]=0 100MHz

BOOT[12:10]=011 100MHz

PCIESSEN=1 1 = PCIe module enabled

PCIESSMODE[1:0]=00 PCIe in End-point mode

thank you,

bai