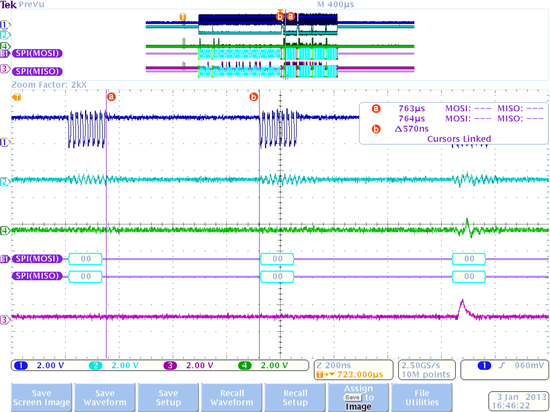

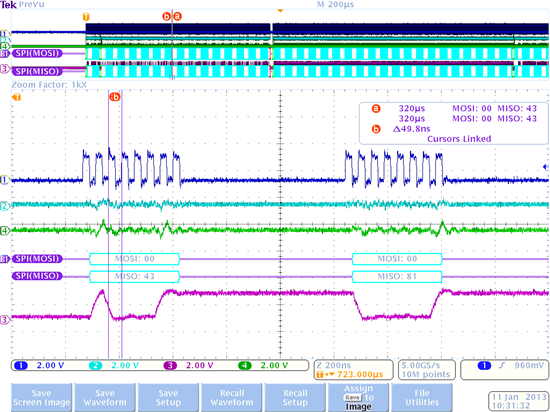

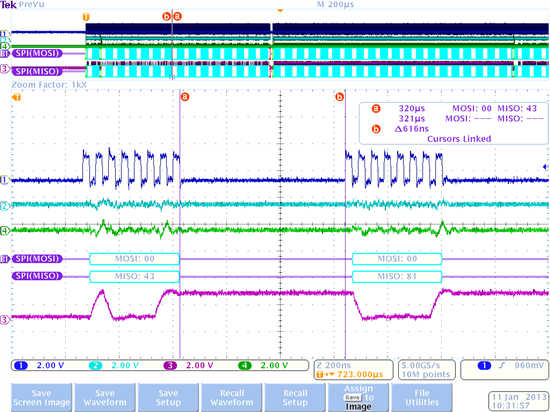

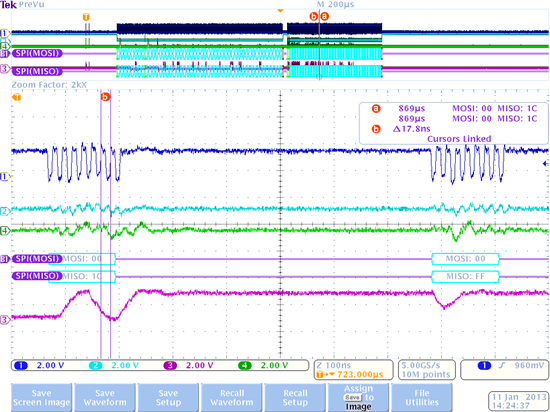

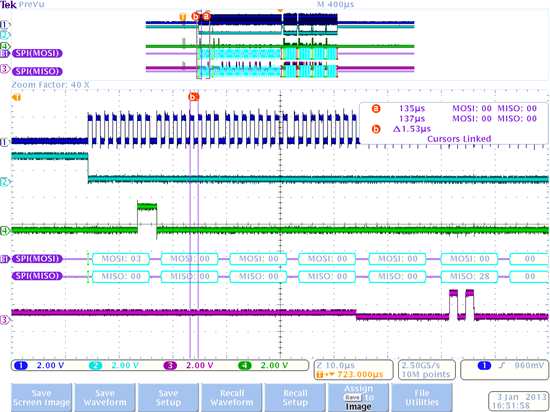

Hi, I wanted to understand if the there is some way to decrease the boot time ( ideally by 2 x to 4 x) needed to read in the ~4MB of app code. We are using the TMSDSEVMC6657 where we are setting the DIP SW so boot mode is SPI . The RBL first reads in the SPI Boot Parameter Table at a slow clock rate ( ~654KHz). This is not a issue since the SPI Boot Parameter Table is small. One of the parameters in the SPI Boot Parameter Table is to set the SPI Bus Speed and we are currently setting this to 50Mhz. Once the SPI Boot Parameter Table is complete , the Boot Table data is being clocked by RBL at ~56MHz ( this part is good) but we are seeing ~ 517usec delay between each byte being read in. The scope image ( see SPI Boot Boot Table.jpg attached) , illustrates the behavior. Is there some way to decrease or eliminate the 517usec delay ( latency) between successive SPI byte reads of the 4MB of code or is there inherent to the RBL operation ? Thank you

Larry

For reference, at the bottom of this note is the SPI Boot Parameter Table data we are using.