Hi,

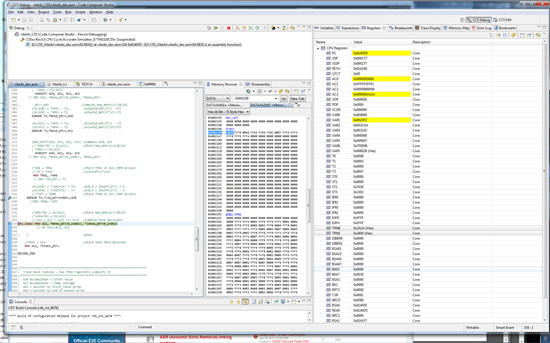

When I debug my code, there are several questions I cannot find the answers. In the following figure, when I stop at line 327, it seems to me that AC1 and AC3 should have the same results as TRN1 and TRN0 (by *AR6 and *AR7 as the comment says). In fact, AC3 is the same with TRN0, but AC1(ignore high 6 bits. fff2h) is not the same with TRN1(2400h). At the XAR6 address(7f000b) content is that of TRN1, i.e. 2400h. At the XAR7 address(000028h) the content is that of TRN0, i.e.2A2Ah.

Then the logic of line 336 is the combination of AC1 and AC3 after AC3 left rotation 8 bits. But either with the TRN0, TRN1, or AC1, AC3, I cannot get the result of FFFA in AC1 after the bits combination. What is the problem with the unexpected results?

Thanks,