Dear support staff

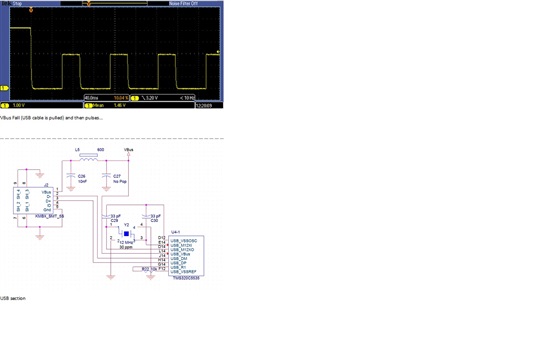

We are working on a device based on the C5535. It seems that when we read the DEVCTL register, the result is always 0x0099 (indicating VBUS_Valid), irrespective of whether the USB bus is present or not.

USBSCR is initialized with 0x2040, so the VBUS detector should be On.

Also the disconnect interrupt or session end interrupt are both not working (probably the same origin...).

In other words, the device has no way of knowing whether or not it is connected to a USB bus...

Is this is known bug?

Thanks

Bruno