Hi Engineers

My system specification is like below

CPU : DM368-432MHz, DDR-360MHz

OS : Non OS

Flash Memory : Both NAND and NOR

CCS : V5.x

We can select NAND/NOR boot using option register -- BTSEL[2:0], AECFG[2:0], CE0, CE1

========

With these environment, i did like below

1. USE NAND Flash Boot Mode : OK

- BTSEL[2:0] = 000, AECFG[2:0] = 0xx

- NAND - CE0, NOR - CE1

- UBL, UBOOT, Application Code reside in NAND

2. USE NOR Flash Boot mode : NG

- BTSEL[2:0] = 001, AECFG[2:0] = 101

- NOR(CE0), NAND(CE1)

- UBL, UBOOT, Application code reside in NOR

--> In this case, if i disable all interrupt then : OK

--> if i enable even only 1 interrupt, IRQ jump to 0x02000018 instead 0x00000018, i made VINTH signal to "L" using CP15 command at boot.asm

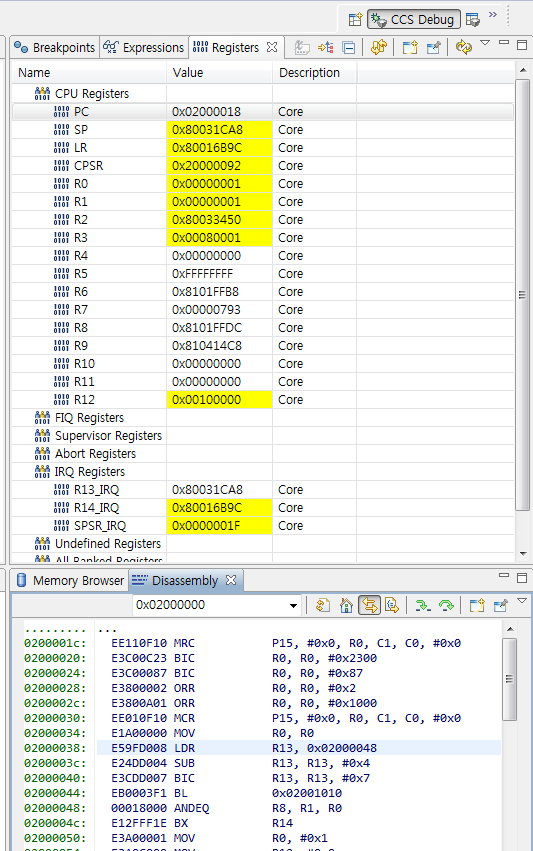

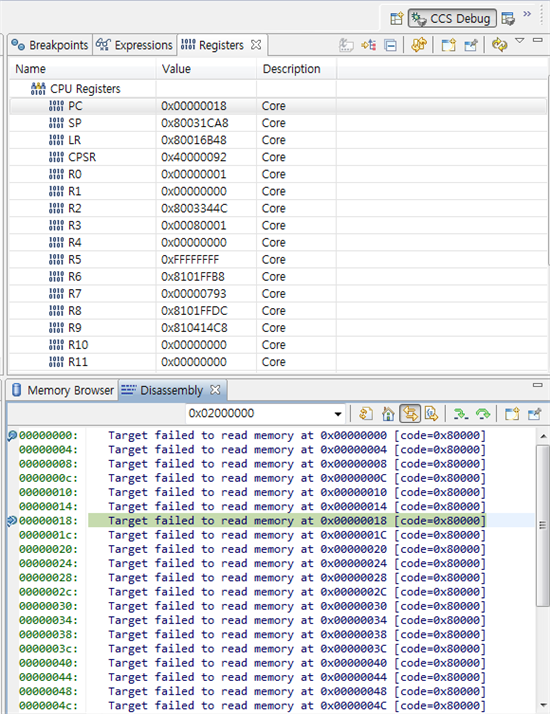

Below is my CCS dump after breakpoint at 0x02000018 using CCS V5.x

Same Board and software, different Boot mode ??

Thanks in advance