All

I am using u-boot-2010.06-psp04.01.00.06.patch1

In drivers/net/Davinci_emac.h,there is a emac_regs definition.

typedef struct {

dv_reg TXIDVER;

dv_reg TXCONTROL;

dv_reg TXTEARDOWN;

u_int8_t RSVD0[4];

dv_reg RXIDVER;

dv_reg RXCONTROL;

dv_reg RXTEARDOWN;

u_int8_t RSVD1[100];

dv_reg TXINTSTATRAW;

dv_reg TXINTSTATMASKED;

dv_reg TXINTMASKSET;

dv_reg TXINTMASKCLEAR;

dv_reg MACINVECTOR;

u_int8_t RSVD2[12];

dv_reg RXINTSTATRAW;

dv_reg RXINTSTATMASKED;

dv_reg RXINTMASKSET;

dv_reg RXINTMASKCLEAR;

dv_reg MACINTSTATRAW;

dv_reg MACINTSTATMASKED;

dv_reg MACINTMASKSET;

dv_reg MACINTMASKCLEAR;

u_int8_t RSVD3[64];

dv_reg RXMBPENABLE;

dv_reg RXUNICASTSET;

dv_reg RXUNICASTCLEAR;

dv_reg RXMAXLEN;

dv_reg RXBUFFEROFFSET;

dv_reg RXFILTERLOWTHRESH;

u_int8_t RSVD4[8];

dv_reg RX0FLOWTHRESH;

dv_reg RX1FLOWTHRESH;

dv_reg RX2FLOWTHRESH;

dv_reg RX3FLOWTHRESH;

dv_reg RX4FLOWTHRESH;

dv_reg RX5FLOWTHRESH;

dv_reg RX6FLOWTHRESH;

dv_reg RX7FLOWTHRESH;

dv_reg RX0FREEBUFFER;

dv_reg RX1FREEBUFFER;

dv_reg RX2FREEBUFFER;

dv_reg RX3FREEBUFFER;

dv_reg RX4FREEBUFFER;

dv_reg RX5FREEBUFFER;

dv_reg RX6FREEBUFFER;

dv_reg RX7FREEBUFFER;

dv_reg MACCONTROL;

dv_reg MACSTATUS;

dv_reg EMCONTROL;

dv_reg FIFOCONTROL;

dv_reg MACCONFIG;

dv_reg SOFTRESET;

u_int8_t RSVD5[88];

dv_reg MACSRCADDRLO;

dv_reg MACSRCADDRHI;

dv_reg MACHASH1;

dv_reg MACHASH2;

dv_reg BOFFTEST;

dv_reg TPACETEST;

dv_reg RXPAUSE;

dv_reg TXPAUSE;

u_int8_t RSVD6[16];

dv_reg RXGOODFRAMES;

dv_reg RXBCASTFRAMES;

dv_reg RXMCASTFRAMES;

dv_reg RXPAUSEFRAMES;

dv_reg RXCRCERRORS;

dv_reg RXALIGNCODEERRORS;

dv_reg RXOVERSIZED;

dv_reg RXJABBER;

dv_reg RXUNDERSIZED;

dv_reg RXFRAGMENTS;

dv_reg RXFILTERED;

dv_reg RXQOSFILTERED;

dv_reg RXOCTETS;

dv_reg TXGOODFRAMES;

dv_reg TXBCASTFRAMES;

dv_reg TXMCASTFRAMES;

dv_reg TXPAUSEFRAMES;

dv_reg TXDEFERRED;

dv_reg TXCOLLISION;

dv_reg TXSINGLECOLL;

dv_reg TXMULTICOLL;

dv_reg TXEXCESSIVECOLL;

dv_reg TXLATECOLL;

dv_reg TXUNDERRUN;

dv_reg TXCARRIERSENSE;

dv_reg TXOCTETS;

dv_reg FRAME64;

dv_reg FRAME65T127;

dv_reg FRAME128T255;

dv_reg FRAME256T511;

dv_reg FRAME512T1023;

dv_reg FRAME1024TUP;

dv_reg NETOCTETS;

dv_reg RXSOFOVERRUNS;

dv_reg RXMOFOVERRUNS;

dv_reg RXDMAOVERRUNS;

u_int8_t RSVD7[624];

dv_reg MACADDRLO;

dv_reg MACADDRHI;

dv_reg MACINDEX;

u_int8_t RSVD8[244];

dv_reg TX0HDP;

dv_reg TX1HDP;

dv_reg TX2HDP;

dv_reg TX3HDP;

dv_reg TX4HDP;

dv_reg TX5HDP;

dv_reg TX6HDP;

dv_reg TX7HDP;

dv_reg RX0HDP;

dv_reg RX1HDP;

dv_reg RX2HDP;

dv_reg RX3HDP;

dv_reg RX4HDP;

dv_reg RX5HDP;

dv_reg RX6HDP;

dv_reg RX7HDP;

dv_reg TX0CP;

dv_reg TX1CP;

dv_reg TX2CP;

dv_reg TX3CP;

dv_reg TX4CP;

dv_reg TX5CP;

dv_reg TX6CP;

dv_reg TX7CP;

dv_reg RX0CP;

dv_reg RX1CP;

dv_reg RX2CP;

dv_reg RX3CP;

dv_reg RX4CP;

dv_reg RX5CP;

dv_reg RX6CP;

dv_reg RX7CP;

} emac_regs;

static volatile emac_regs *adap_emac = (emac_regs *)0x4A100000;

It looks the same with c6748's emac register ,but confict with DM8148's

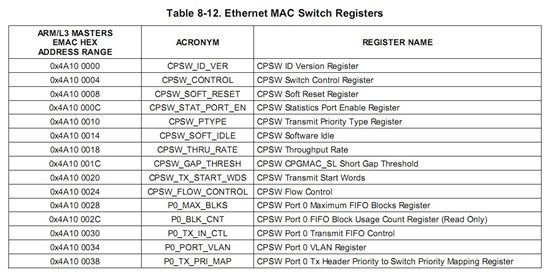

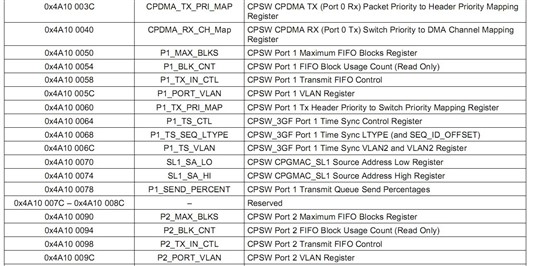

Fllow is the 8148 emac register

the 4A10 000C is cpsw_stat_port_en,but the register is reserved .