Hello.

I am gonna use DDR2 as memory of AM335x system.

On datasheet Figure5-38(sprs717e P155), it specifies that the CKE pin and ODT pin are connected between AM335x and DDR2 immediately.

Is it no problem that it does not exist pulldown resister?

Since the datasheet specifies the "BALL RESET STATE", I understand that CKE and ODT pin hold Low state after AM335x power up.

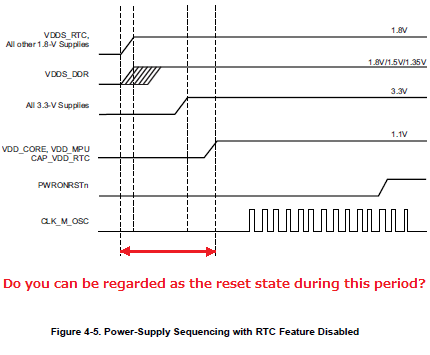

But, I am taking care about before completion of AM335x power up.

Because, AM335x needs the power up sequence: 1.8V --> 3.3V --> 1.1V

My question is:

Are the CKE and ODT held on Low state during power up?

Does it not needed pulldown resister?

Best regards, RY