Hello,

I would like to ask you about High-Speed Bypass Capacitors of AM335x.

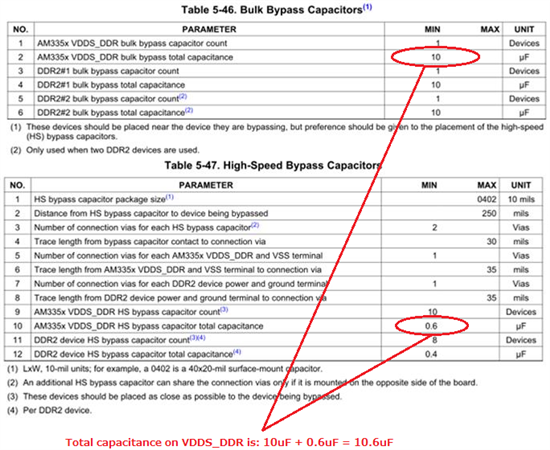

a) There is description Datasheet Table 3-13(sprs717e: P91).

It specifies that CVDDS_DDR is 10.06uF :

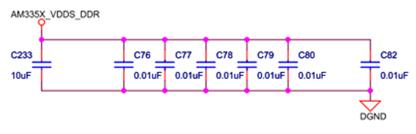

And the capacitance on AM3358EVM is below (it is match the spec of Table 3-13):

b) On the other hand, there is description about DDR2(sprs717e: P160).

It specifies that the total capacitance on VDDS_DDR is 10.6uF. (It is NOT 10.06uF.)

Which is correct, a) or b) ?

c) On table 5-47, the No.12 specifies that the total capacitance is 0.4uF.

But, The capacitance on AM3358EVM is NOT 0.4uF. (It is total 0.08uF by 8 capacitors on EVM)

Would you let me know the correct capacitance value?

Best regards, RY