hi there

May be someone have similar trouble or can suggest any idea?

Problem description:

After linux host boots, "lspci -n" don't show the TI board. If I push "Full Reset" on TI board several times, then issue "echo 1 > /sys/bus/pci/rescan",

I could see the board:

lspci -v -d 104c:*

01:00.0 Multimedia controller: Texas Instruments Device b005 (rev 01)

Flags: bus master, fast devsel, latency 0, IRQ 16

Memory at 80900000 (32-bit, non-prefetchable) [size=1M]

Memory at 82400000 (32-bit, prefetchable) [size=512K]

Memory at 82000000 (32-bit, prefetchable) [size=4M]

Memory at 81000000 (32-bit, prefetchable) [size=16M]

Memory at 82490000 (32-bit, prefetchable) [size=4K]

Memory at 82480000 (32-bit, prefetchable) [size=64K]

Capabilities: [40] Power Management version 3

Capabilities: [50] MSI: Enable- Count=1/1 Maskable- 64bit+

Capabilities: [70] Express Endpoint, MSI 00

Capabilities: [100] Advanced Error Reporting

The attempt to execute PCIe demo fails (insmod hangs up), the command is "insmod pciedemo.ko".

After some debug I found the exact place where demo hangs:

<pciedemo.c>

#if HELLO_WORLD_DEMO

/* Load DDR init code into DSP */

pushData(ddrInitCode, 0, &bootEntryAddr);

/* Write boot entry address into MAGIC_ADDR */

writeDSPMemory(0, MAGIC_ADDR, &bootEntryAddr, 4);

while (1) {

/* <<<<< Here this demo hangs forever >>>>>*/

readDSPMemory(0, MAGIC_ADDR, buffer, 4);

if (buffer[0] == 0) break;

for (i = 0; i < 1000; i++) i++;

}

/* Load "Hello World" demo into DSP */

pushData(bootCode, 9, &bootEntryAddr);

/* Write boot entry address into MAGIC_ADDR */

writeDSPMemory(0, MAGIC_ADDR, &bootEntryAddr, 4);

#endif

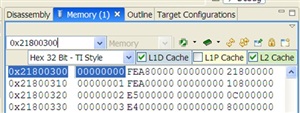

Also any attempt to read from TI device’s memory by means of io-mem returns 0xffffffff. I. e. any pci memory access, directly, or through

linux API ("ioread32()") returns only FFs. But I can read and write all the config space and application registers by means of io-port access.

I. e. linux functions like"pci_read_config_dword()" are works fine.

My conclusion: the inbound address translation or memory access via PCIe is not working, while io-port access to entire PCIe config

space is working, but not stable. I checked all the BAR and IB_XXX register contents, all values were set according to the manual.

Here some details:

Board Name: TMDXEVM6678LE Rev 1.0 / PCB Rev A102-1

Board Serial Number: EPD0061817

Board additions: AMC to PCIe Adapter, BlackHawk XDS560v2 USB Mezzanine

AMC to PCIe S/N: 0058 PCB REV: 17-00107-03 PCA REV: 18-00107-03

DIP switch configuration:

SW3: (off, on, on, off)

SW4: (on, on, on, on)

SW5: (on, on, on, off)

SW6: (off, on, on, on)

SW9: (off/on, on)

Firmware used: MCSDK_02_01_02_06

Linux on the host - tried SuSe 11.3 and Ubuntu 10.2

Board POST test completes succesfully.

I also read and tried all suggestions in

http://e2e.ti.com/support/dsp/c6000_multi-core_dsps/f/639/t/247997.aspx

with no positive result.

Regards,

Dmytro