Hi, Everyone!

According Hyperlink data mannual, the throughput of hyperlink should be 40gbps with 4 lanes when each of lane configured 10Gbps.

But when i test this throughput with edma cc1 from c6670 to c6678, the result is around 20Gbps instead of 40Gbps. the configuration is as below,

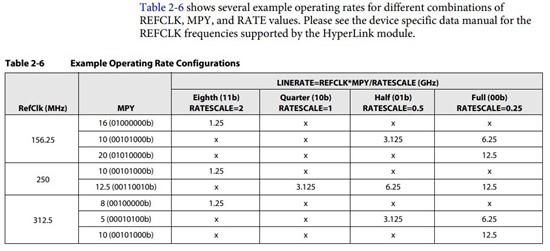

1) serdes reference clock: 250Mhz

2) pll mpy is 10x and full speed is configured, so line rate per lane is 250*40 = 10Gbps.

3) 4 lanes are actived.

3) EDMA cc1, Acnt = 31KB, Bcnt = 100.

Then i use edma move 3100KB data from c6670 to a 6678 buffer , which address is mapped into hyperlink space.

The result is thoughput of hyperlink inter-dsp ddr-to-ddr is 20.8Gbps, while throughput of intra-dsp ddr-to-ddr edma cc1 is 39Gbps.

I am confused by this result, i know in hyperlink module the 8b9b encoding and mac control header may reduce some throughput, and it maybe

40Gbps * 8/9 * 31/32 = 34.44Gbps (1 control packet every 32 packets.)

So, i think my result of 20.8Gbps is not correct anyway.