Hi,

I'm using a TMDSSK3358 board and checking the schematic of it.

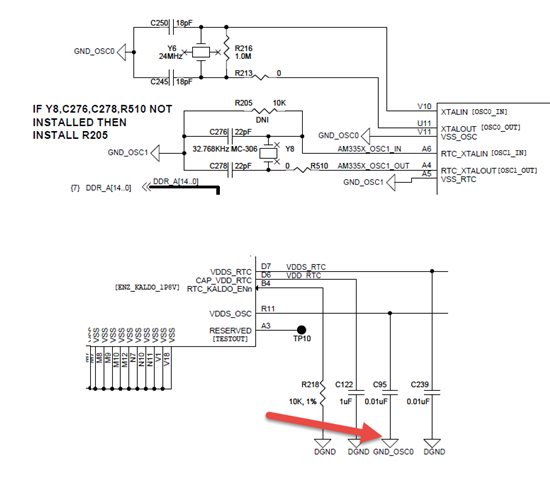

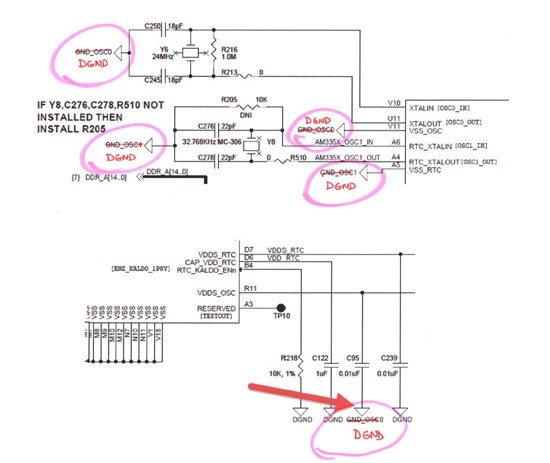

VDDS_OSC is connected to VSS_OSC (GND_OSC0) through a bypass capacitor, but VDDS_RTC is connected to DGND through a bypass capacitor.

Should VDDS_RTC be connected to VSS_RTC (GND_OSC1) through a bypass capacitor?

And, is the ground of VRTC VSS_RTC?

Thanks

Nomoto