Hello,

I would like to clarify about the PORz time after boot-up.

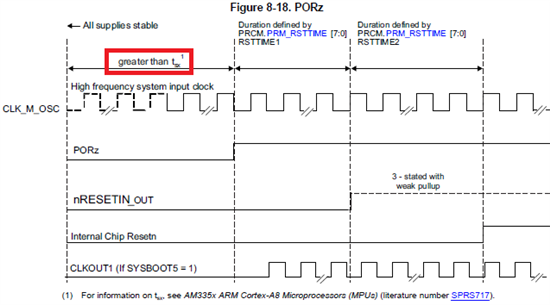

I have refered the AM335x TRM Figure 8-18(spruh73g: P533).

There is the description that PORz have to be greater than tsx.

But, I know that the tsx is requirement of Crystal circuit.

Since the crystal circuit have been already stable after boot-up, I think it is not requirement of PORz after boot-up.

I need the MIN time of PORz after boot-up.

May I have the following answer:

- Where is the requirement of PORz after boot-up?

- The tsx is TYP value. After boot-up, can I think it is MIN time for PORz requirement? (Bacause the crystal circuit have been already stable.)

Best regards, RY