Hi.

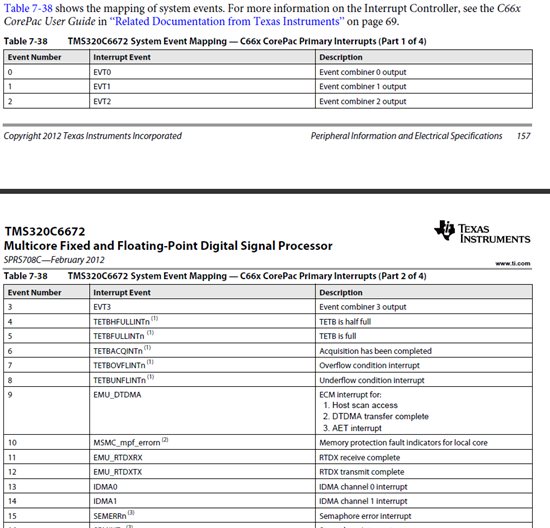

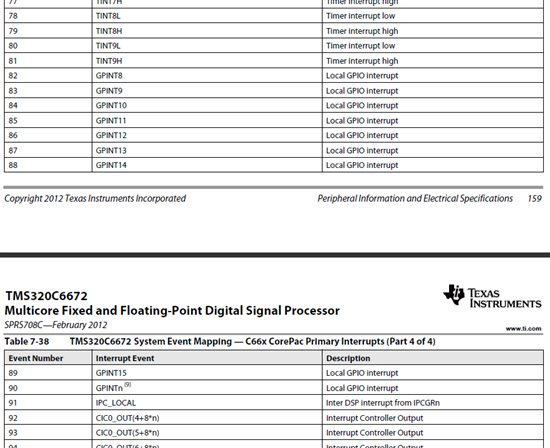

Section 7.9 in TMS320C6672 data maual illustrates that the event number of GPINTn is 90 and 'n' is the CorePac number.

Does that mean it is impossible to make GPIO2 ~ GPIO7 as interrupt sources on TMS320C6672 board?

Or, if there is a way, please let me know.

Thanks.