We have a C6655 configured as an endpoint that we are trying to initialize its PLL2 and DDR3 over the PCIe interface by the root port using a similar process found in the evm gel scripts so that we can download its application code to DDR3 and run.

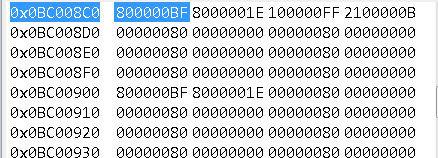

I am having problems with configuring the PLL2 and DDR3 registers. I have tried to "unlock" the KICK0 and KICK1 registers accordingly but it appears that my PCIe writes to the C6655 over PCIe are not working. I know I have set my address translation tables correctly as the read operation for these registers appear to be correct and returning reasonable values.

1: Can the KICK registers be unlocked by the root port over PCIe ?

2: Can the PLL2 and DDR3 registers be configured over PCIe or only by the Local C6655 Core 0 ?

3: Do we need to configure PLL1 and other things in order to setup the PLL2 and DDR3 ? (we think the default PLL1 would work for us)

Can you please answer the above questions and provide som further suggestions into this problem.

Thanks