Dear all,

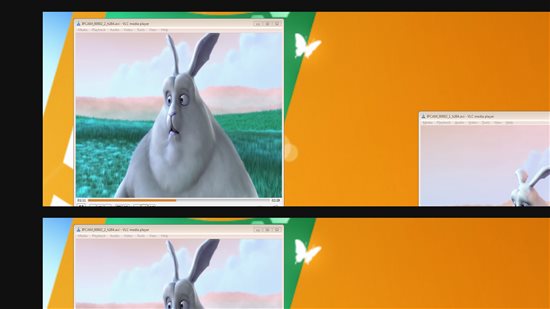

I am using a custmo Dm814x board and can capture using V4L2. My input is a 1920x1080p60 24-bit RGB source with discrete syncs. I capture the image below which is ok for 720 lines and then possibly then start of the next frame has been DMA'd into my buffer.

I've checked and the VIDIOC_G_FMT ioctl is returning the correct data, the capture is setup for a 1920x1080 buffer. It looks to me like the VIP is limited to capture 720 lines?

Does anybody know where a value for this may be defined? I'm guessing it's in the VIP Port Config but there doesn't seem to be a limit on the number of lines to capture?

Help appreciated.

Regards,

Danny Cullen