Hi all,

In one audio product, we have 2 audio input channels L&R, and 5 audio output channels including L&R, LS&RS, and bass. And we use 4 AXR0[n] pins, 1 for input, and 3 for output.

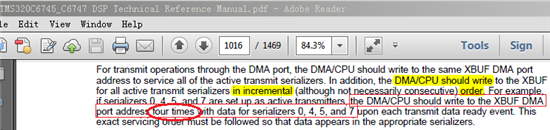

In “TMS320C6745_C6747 DSP Technical Reference Manual.pdf” P1016 there is one sentence I don’t understand, which is highlighted in red circle. It says “the DMA/CPU should write to XBUF DMA port address four times with data for serializers 0, 4, 5, and 7”. I don’t quite know what does “four times” mean since there is one DMA event each time, and all data is transferred at once. How to write data “four times” as it states?

My understanding is that on each Tx DMA event, I should write 3 words data to DMA port once time. That’s all. I couldn’t imagine how to write data four times.

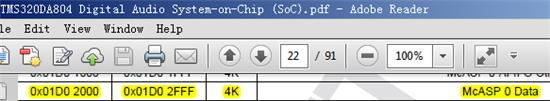

In a snapshot below, we can see McASP 0 data ranges from 0x01D0 2000 – 0x01D0 2FFF, 4KB size. Does it mean we should put all serializers data within the 4K memory space? And for DMA operation, we should only write to one constant DMA port address, which is 0x01D0 2000, right?