Hi,

I am currently testing the TSIP on a prototype board with the C6678 DSP. The test I am implementing involves connecting all the TSIP signals to an FPGA and looping the TX data signals from the DSP back onto the RX signals back to the DSP.

The FPGA provides a 16.384MHz clock to each clock pin on the DSP and a Frame Sync signal that pulses from high to low every 2048 clock cycles. The frame sync signal is sent to each FS pin on the DSP.

I run the test project "TSIP_testProject" provided in the C6678 PDK package to test my setup with the following configuration settings:

/* Provide size information for TSIP */

sizeCfg->maxChannels = TSIP_MAX_TIMESLOTS;

sizeCfg->subFrameSize = 8;

sizeCfg->wordSize = 8;

/* Global configuration */

cfg->testMode = FALSE;

cfg->testModeSelect = CSL_TSIP_TESTMODE_DATA_LOOPBACK;

cfg->clkRedund = CSL_TSIP_CLKD_REDUN;

cfg->endian = CSL_TSIP_ENDIAN_LITTLE;

cfg->priority = CSL_TSIP_PRI_0;

cfg->maxPriority = CSL_TSIP_PRI_0;

cfg->sizeCfg = sizeCfg;

cfg->maxPhase = 10;

cfg->subFrameCallout=NULL;

cfg->cxt=NULL;

/* Transmit configuration */

cfg->tx.channel = deviceWhoAmI();

cfg->tx.frameSize = CSL_TSIP_FRAMESIZE_128;

cfg->tx.tsPerFrame = 256;

cfg->tx.clkSrc = CSL_TSIP_CLKSRC_A;

cfg->tx.dataDelay = 0;

cfg->tx.bdxDelay = CSL_TSIP_DLY_CTRL_DISABLE;

cfg->tx.idleDrive = CSL_TSIP_XMTDIS_HIGHIMP;

cfg->tx.fsyncPol = CSL_TSIP_FSYNCP_ALOW;

cfg->tx.fsyncClkPol = CSL_TSIP_CLKP_RISING;

cfg->tx.clkPol = CSL_TSIP_CLKP_FALLING;

cfg->tx.dataRate = CSL_TSIP_DATARATE_8M;

cfg->tx.clkMode = CSL_TSIP_CLKM_DBL;

cfg->tx.superFrameInt = CSL_TSIP_INT_ACK;

cfg->tx.frameInt = CSL_TSIP_INT_ACK;

cfg->tx.frameIntDelay = 0;

/* Receive configuration */

cfg->rx.channel = deviceWhoAmI();

cfg->rx.frameSize = CSL_TSIP_FRAMESIZE_128;

cfg->rx.tsPerFrame = 256;

cfg->rx.clkSrc = CSL_TSIP_CLKSRC_A;

cfg->rx.dataDelay = 0;

cfg->rx.bdxDelay = CSL_TSIP_DLY_CTRL_DISABLE;

cfg->rx.fsyncPol = CSL_TSIP_FSYNCP_ALOW;

cfg->rx.fsyncClkPol = CSL_TSIP_CLKP_FALLING;

cfg->rx.clkPol = CSL_TSIP_CLKP_RISING;

cfg->rx.dataRate = CSL_TSIP_DATARATE_8M;

cfg->rx.clkMode = CSL_TSIP_CLKM_DBL;

cfg->rx.superFrameInt = CSL_TSIP_INT_ACK;

cfg->rx.frameInt = CSL_TSIP_INT_ACK;

cfg->rx.frameIntDelay = 0;

/* Size of application buffers */

#define BUFSIZE_APP 40*22 /*must be a multiple of the tx.frameSize (40).

Due to L2 memory size, max value for this define is 880*/

/* Number of TSIP ports used in the test */

#define NUM_USED_TSIP_PORTS 2

/* This test uses the same number of time slots per TSIP port being tested*/

/* Number of used time slots per TSIP port (same for all ports)*/

#define NUM_USED_TIME_SLOTS 32

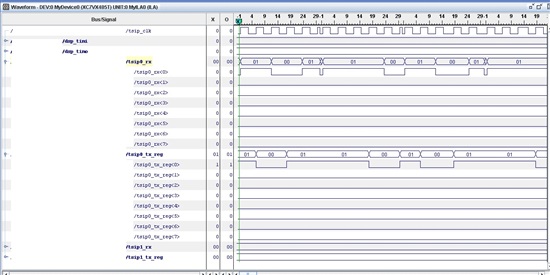

With these settings, I pass the tests on both TSIP ports on the DSP. However, when I scope the TSIP pins on my hardware, I only have one active link on both the TX and RX lines. I would have thought that there would have been 8 active links when I have a 16.384MHz clock and specified a 8.192 Mbps data rate?

Would there be an issue with my frame sync signal? It specifies in the TSIP user guide (SPRUGY4) that for 8.192 Mbps operation, there are 1024 clocks per frame in single-rate clock mode and 2048 clocks per frame in double-rate clock mode, so I presume it should be fine.

I have specified 256 timeslots per frame and considering that each serial interface link supports 8-bit timeslots, does this mean that it is not necessary to operate the other links?

Am I right in thinking that I need to reduce the number of timeslots per frame? If I do, then should I not also need to reduce the frame sync pulse rate?

Regards,

Fearghal