Hey,

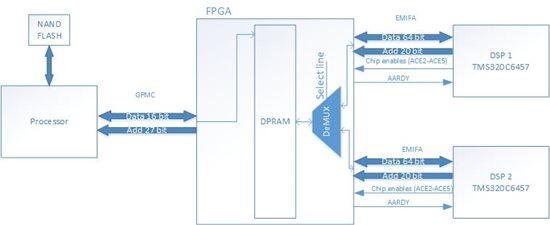

I have a design where 4 DSPs (TMS3206457) are interfaced with ALTERA FPGA through EMIFA interface. I have designed t he board such that the default boot mode selection is EMIF. The power is given simultaneously to all the 4 DSPs. The design does not contain dedicated FLASH device for each DSP, hence the DSP gets its code frm the DPRAM on the FPGA. I am planning to keep a single DPRAM in the FPGA, and by using a MUX inside the FPGA to select the DSP EMIFA data and address lines to select each DSPs. Now, when i am loading the code for DSP1, will the other DSPs be waiting for the data so tat it automatically takes the data when i change the selection line to 2nd DSP or should i control the DSP using the POR??