Hi all,

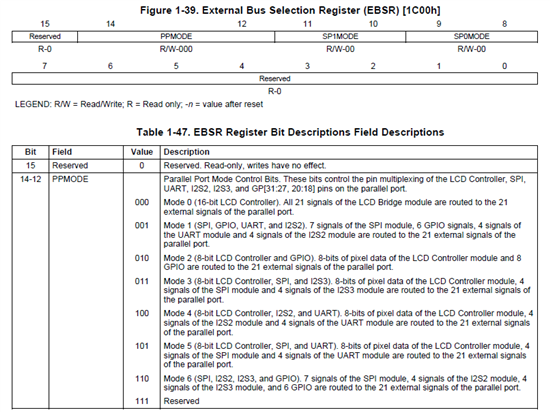

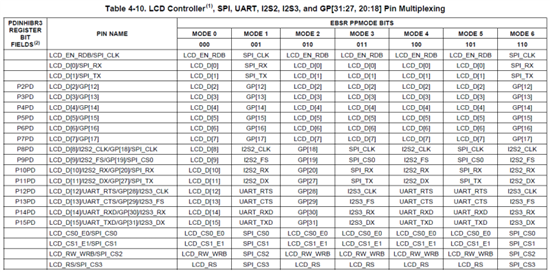

I did not find the way to define the SPI lines routing to connector J13 (extension).

From the board schematics they are shared (including SPI_CS0) between LCD, SPI EPROM and Digital Extension header (J13),

but is not clear how to define the routing.

Thanks in advance for any suggestion,

Rubby