Hi ,

I want to run the openMP Hello World Example . I have follow these steps after create a Project:

- . run Gel File on Core 0 , Core 1 , Core 2 and Core 3

- . run Global Setup on Core 0

- . Load the Programm on Core 0 , Core 1 , Core 2 and Core 3

C66xx_0: GEL Output: Setup_Memory_Map...

C66xx_0: GEL Output: Setup_Memory_Map... Done.

C66xx_0: GEL Output: C6678L GEL file Ver is 2.005

C66xx_0: GEL Output: Global Default Setup...

C66xx_0: GEL Output: Setup Cache...

C66xx_0: GEL Output: L1P = 32K

C66xx_0: GEL Output: L1D = 32K

C66xx_0: GEL Output: L2 = ALL SRAM

C66xx_0: GEL Output: Setup Cache... Done.

C66xx_0: GEL Output: Main PLL (PLL1) Setup ...

C66xx_0: GEL Output: PLL in Bypass ...

C66xx_0: GEL Output: PLL1 Setup for DSP @ 1000.0 MHz.

C66xx_0: GEL Output: SYSCLK2 = 333.3333 MHz, SYSCLK5 = 200.0 MHz.

C66xx_0: GEL Output: SYSCLK8 = 15.625 MHz.

C66xx_0: GEL Output: PLL1 Setup... Done.

C66xx_0: GEL Output: Power on all PSC modules and DSP domains...

C66xx_0: GEL Output: Security Accelerator disabled!

C66xx_0: GEL Output: Power on all PSC modules and DSP domains... Done.

C66xx_0: GEL Output: PA PLL (PLL3) Setup ...

C66xx_0: GEL Output: PA PLL Setup... Done.

C66xx_0: GEL Output: DDR3 PLL (PLL2) Setup ...

C66xx_0: GEL Output: DDR3 PLL Setup... Done.

C66xx_0: GEL Output: DDR begin (1333 auto)

C66xx_0: GEL Output: XMC Setup ... Done

C66xx_0: GEL Output:

DDR3 initialization is complete.

C66xx_0: GEL Output: DDR done

C66xx_0: GEL Output: DDR3 memory test... Started

C66xx_0: GEL Output: DDR3 memory test... Passed

C66xx_0: GEL Output: PLL and DDR Initialization completed(0) ...

C66xx_0: GEL Output: configSGMIISerdes Setup... Begin

C66xx_0: GEL Output:

SGMII SERDES has been configured.

C66xx_0: GEL Output: Enabling EDC ...

C66xx_0: GEL Output: L1P error detection logic is enabled.

C66xx_0: GEL Output: L2 error detection/correction logic is enabled.

C66xx_0: GEL Output: MSMC error detection/correction logic is enabled.

C66xx_0: GEL Output: Enabling EDC ...Done

C66xx_0: GEL Output: Configuring CPSW ...

C66xx_0: GEL Output: Configuring CPSW ...Done

C66xx_0: GEL Output: Global Default Setup... Done.

C66xx_1: GEL Output: Setup_Memory_Map...

C66xx_1: GEL Output: Setup_Memory_Map... Done.

C66xx_2: GEL Output: Setup_Memory_Map...

C66xx_2: GEL Output: Setup_Memory_Map... Done.

C66xx_3: GEL Output: Setup_Memory_Map...

C66xx_3: GEL Output: Setup_Memory_Map... Done.

C66xx_0: GEL Output: Invalidate All Cache...

C66xx_0: GEL Output: Invalidate All Cache... Done.

C66xx_0: GEL Output: GEL Reset...

C66xx_0: GEL Output: GEL Reset... Done.

C66xx_0: GEL Output: Disable all EDMA3 interrupts and events.

C66xx_1: GEL Output: Invalidate All Cache...

C66xx_1: GEL Output: Invalidate All Cache... Done.

C66xx_1: GEL Output: GEL Reset...

C66xx_1: GEL Output: GEL Reset... Done.

C66xx_2: GEL Output: Invalidate All Cache...

C66xx_2: GEL Output: Invalidate All Cache... Done.

C66xx_2: GEL Output: GEL Reset...

C66xx_2: GEL Output: GEL Reset... Done.

C66xx_3: GEL Output: Invalidate All Cache...

C66xx_3: GEL Output: Invalidate All Cache... Done.

C66xx_3: GEL Output: GEL Reset...

C66xx_3: GEL Output: GEL Reset... Done.

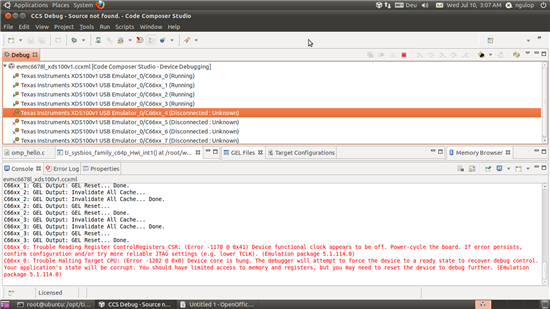

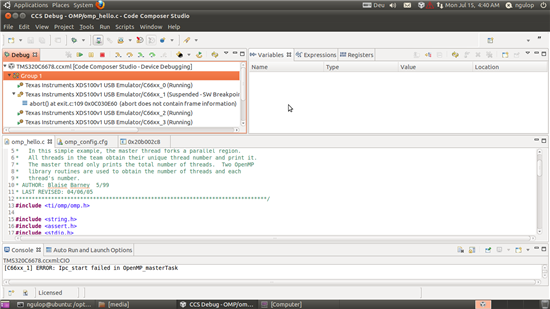

the Resume Button to run the Application is not activ after loading the Programm on the Cores , and CCS out that Error ( See Picture)

I use omp_1_01_03_02 .

I attached the Output from CCS , What is wrong?

Thank you for reply

Lopez