Hi,

Since I just want the Digital inputs and Digital outputs, so I modify the tiescappl.h of the 1.0.0.8 SDK.

Remove the AI and Motor Outputs and modify the XML file too.

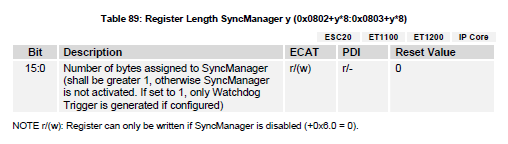

But when I used the TwinCAT and want to active free run the "TI_ESC" device, but It always get the 0x001b value of AL status code (0x134:0x135).

TI_ESC can't change the Safe-OP to OP mode, because the Process Data Watchdog expired.

Have any suggestion?

Following is the codes.

/******************************************************************************

* Object 0x1C12: RxPDO assignment

******************************************************************************/

#ifdef _OBJD_

OBJCONST TSDOINFOENTRYDESC OBJMEM asEntryDesc0x1C12[] = {

{DEFTYPE_UNSIGNED8, 0x08, ACCESS_READ},

{DEFTYPE_UNSIGNED16, 0x10, ACCESS_READ}};

//{DEFTYPE_UNSIGNED16, 0x10, ACCESS_READ}};

OBJCONST UCHAR OBJMEM aName0x1C12[] = "RxPDO assign";

#endif //#ifdef _OBJD_

typedef struct STRUCT_PACKED_START {

UINT16 u16SubIndex0;

UINT16 aEntries[1];

} STRUCT_PACKED_END

TOBJ1C12;

PROTO TOBJ1C12 sRxPDOassign

#ifdef _TIESC_HW_

= {0x01, {0x1601}}//, 0x1602}}

#endif

;

/******************************************************************************

* Object 0x1C13: TxPDO assignment

******************************************************************************/

#ifdef _OBJD_

OBJCONST TSDOINFOENTRYDESC OBJMEM asEntryDesc0x1C13[] = {

{DEFTYPE_UNSIGNED8, 0x08, ACCESS_READ},

{DEFTYPE_UNSIGNED16, 0x10, ACCESS_READ}};

//{DEFTYPE_UNSIGNED16, 0x10, ACCESS_READ}};

OBJCONST UCHAR OBJMEM aName0x1C13[] = "TxPDO assign";

#endif //#ifdef _OBJD_

typedef struct STRUCT_PACKED_START {

UINT16 u16SubIndex0;

UINT16 aEntries[1];

} STRUCT_PACKED_END

TOBJ1C13;

PROTO TOBJ1C13 sTxPDOassign

#ifdef _TIESC_HW_

= {0x01, {0x1A00}}//, 0x1A03}}

#endif

;

#ifdef _OBJD_

/*if _PIC18 is enabled the object dictionary is fixed defined in coeappl.c*/

TOBJECT OBJMEM ApplicationObjDic[] = {

/* Object 0x1601 */

{NULL,NULL, 0x1601, {DEFTYPE_PDOMAPPING, 8 | (OBJCODE_REC << 8)}, asEntryDesc0x1601, aName0x1601, &RxPDOMap, NULL, NULL, 0x0000 },

/* Object 0x1602 */

// {NULL,NULL, 0x1602, {DEFTYPE_PDOMAPPING, 3 | (OBJCODE_REC << 8)}, asEntryDesc0x1602, aName0x1602, &RxPDO1Map, NULL, NULL, 0x0000 },

/* Object 0x1A00 */

{NULL,NULL, 0x1A00, {DEFTYPE_PDOMAPPING, 8 | (OBJCODE_REC << 8)}, asEntryDesc0x1A00, aName0x1A00, &TxPDOMap, NULL, NULL, 0x0000 },

/* Object 0x1A03 */

// {NULL,NULL, 0x1A03, {DEFTYPE_PDOMAPPING, 2 | (OBJCODE_REC << 8)}, asEntryDesc0x1A03, aName0x1A03, &sAITxPDO1Map, NULL, NULL, 0x0000 },

/* Object 0x1C12 */

{NULL,NULL, 0x1C12, {DEFTYPE_UNSIGNED16, 1 | (OBJCODE_ARR << 8)}, asEntryDesc0x1C12, aName0x1C12, &sRxPDOassign, NULL, NULL, 0x0000 },

/* Object 0x1C13 */

{NULL,NULL, 0x1C13, {DEFTYPE_UNSIGNED16, 1 | (OBJCODE_ARR << 8)}, asEntryDesc0x1C13, aName0x1C13, &sTxPDOassign, NULL, NULL, 0x0000 },

/* Object 0x6000 */

{NULL,NULL, 0x6000, {DEFTYPE_RECORD, 8 | (OBJCODE_REC << 8)}, asEntryDesc0x6000, aName0x6000, &sDIInputs, NULL, NULL, 0x0000 },

/* Object 0x6020 */

// {NULL,NULL, 0x6030, {DEFTYPE_RECORD, 2 | (OBJCODE_REC << 8)}, asEntryDesc0x6030, aName0x6030, &sAI1Inputs, NULL, NULL, 0x0000 },

/* Object 0x7010 */

{NULL,NULL, 0x7010, {DEFTYPE_RECORD, 8 | (OBJCODE_REC << 8)}, asEntryDesc0x7010, aName0x7010, &sDOOutputs, NULL, NULL, 0x0000 },

/* Object 0x7020 */

// {NULL,NULL, 0x7020, {DEFTYPE_RECORD, 3 | (OBJCODE_REC << 8)}, asEntryDesc0x7020, aName0x7020, &sDO1Outputs, NULL, NULL, 0x0000 },

{NULL,NULL, 0xFFFF, {0, 0}, NULL, NULL, NULL, NULL, NULL, 0x0000}};

#endif //#ifdef _OBJD_

Best regards,

Louis chou