Other Parts Discussed in Thread: AM3359

Hi,

I have the following GPMC configuration on a AM3359 device (Silicon Rev 2.0):

- NOR Flash attached to CS0 of GPMC with multiplexed address/data bus (exactly as on the AM335x ICE board)

- MMU and cache enabled for memory except for NOR flash

- NOR flash is mapped to address 0x08000000

and the following code:

volatile Uint16 *pmem16;

while(1==1)

{

pmem16=(Uint16*)0x08000000;

*(pmem16+0x00555)=0x00AA;

*(pmem16+0x002AA)=0x0055;

*(pmem16+0x00555)=0x0090;

ManufacturerCode=*(pmem16+0x00000);

DeviceCode=*(pmem16+0x00001);

BlockProtectionStatus=*(pmem16+0x00002);

}

This code does put the NOR Flash into "AutoSelect" mode and reads manufacturer code, device code and block protection status of first block.

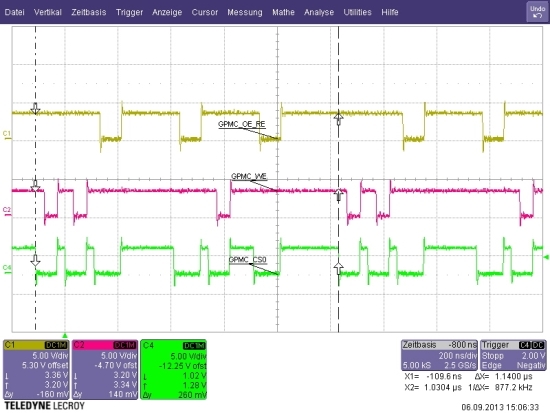

The code works fine if I step over the code in CCS and the signals on the scope look as they should.

But if I let the code run in an endless loop then three writes gets interrupted by some of the read operations and therefore the NOR flash does not switch into "AutoSelect" mode. How can I make shure that all the write operations to the NOR flash are all executed before the read operations are done?

Does this has to do with the L3 Slow Interconnect Interface and the pipelined interface?

Best regards,

Patrick