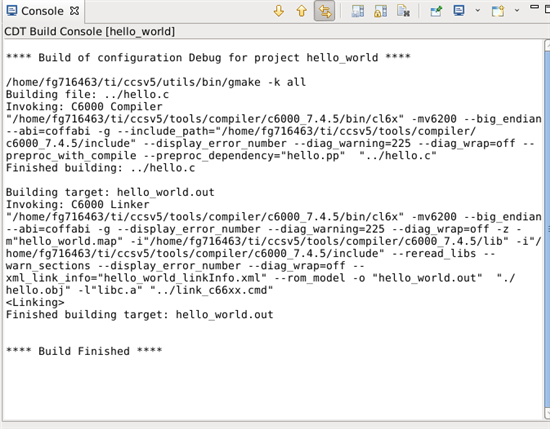

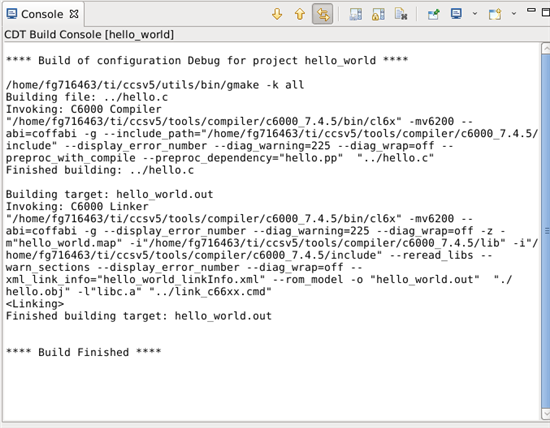

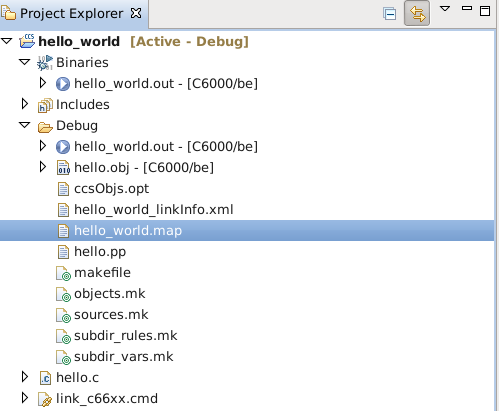

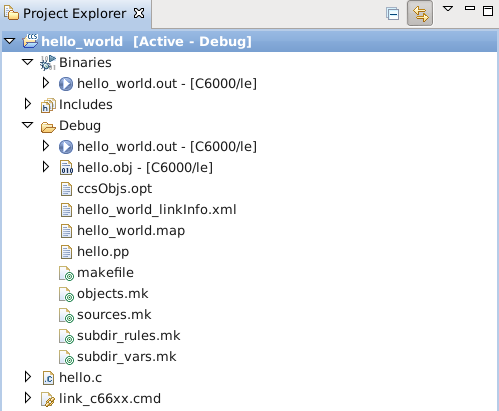

I tried building the hello world program from the CCS, but after building it I get

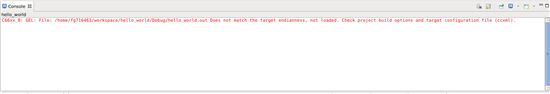

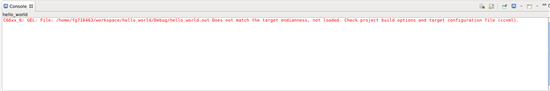

C66xx_6: GEL: File: /home/fg716463/workspace/hello_world/Debug/hello_world.out Does not match the target endianness, not loaded. Check project build options and target configuration file (ccxml).

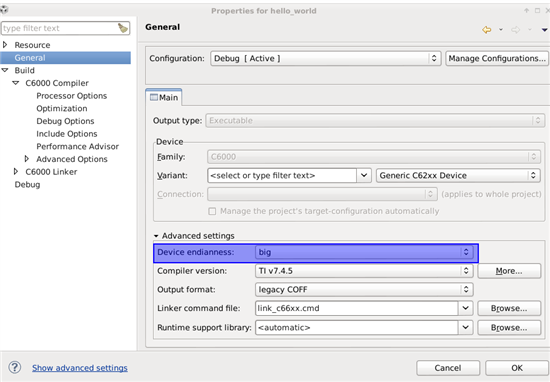

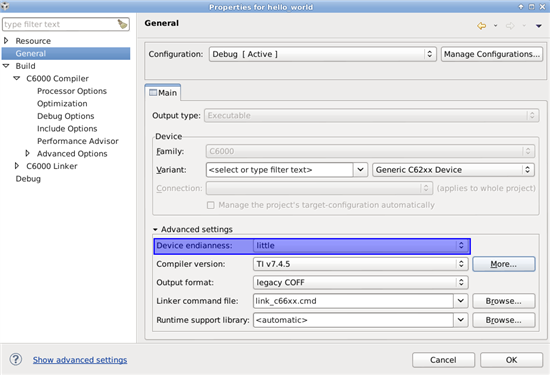

I tried switching "Device endianess" in Properties - General - Advanced Settings, but neither little nor big seem to be working.

As for the target configuration file I did not find where to set the endianess.

Can somebody point me out to what I am doing wrong?