Hello.

I am using UART with FIFO mode.

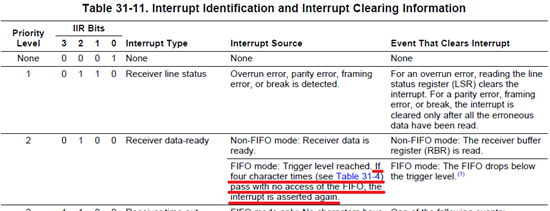

The TRM(P1482: Table31-11) describes about IIR INTID:

If four character times (see Table 31-4) pass with no access of the FIFO, the interrupt is asserted again.

Although I tried to monitor INTID regs EVTFLAG when I got 1st Receiver data-ready, I can not get another interrupt flag.

My question is:

1. How can I get this second interrupt?

2. What kind of interrupt is asserted? (I think it is INTID=010b : Receiver data-ready)

If you need test code of this, coule you let me know.

I can attach it.

Best regards, RY