Hi,

I am using C6748 and AISgen for D800K008 v1.11. If I am correct maximum SPI clock was SYSCLK2 / 3, so if DSP runs at 300 MHz then maximum SPI clock is 300/2/3 = 50 MHz. Problem is that this is maximum clock allowed in AISgen, however if DSP clock is increased to 456 MHz, then SPI clock should also increase to 76 MHz. But AISgen does not allow anything above 50 MHz.

I am using SPI flash that allows clocks upto 108 MHz, therefore it would be significant decrease in boottime if 76 MHz can be used instead of 50 MHz.

Is there a way to bypass this issue somehow, it seems to be bug in AISgen logic.

Andres

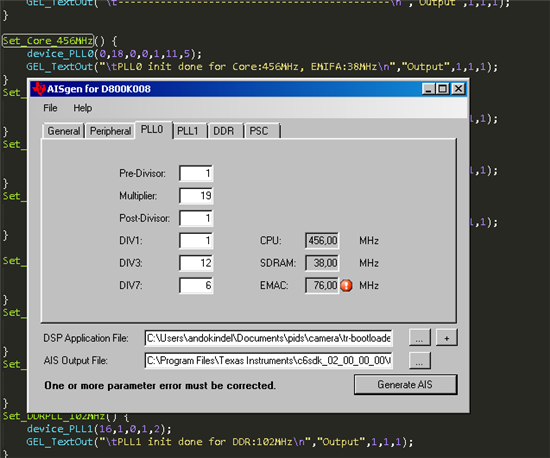

EDIT: AISGen seems to be build for 300 MHz operation (there are couple of places where clock max value could be 50 MHz instead of 76 MHz), because also in PLL0 tab I am unable to use the same settings defined in LCDK gel file for 456 MHz operation.

device_PLL0(0,18,0,0,1,11,5);

device_PLL0(unsigned int CLKMODE, unsigned int PLLM, unsigned int POSTDIV,unsigned int PLLDIV1, unsigned int PLLDIV2, unsigned int PLLDIV3, unsigned int PLLDIV7 )

I cannot put them AISgen, it says that for EMAC it must be number between 1.0 and 50.0: