Hi,

we encounter a problem when our C6678 boards boot with SPI nor-Flash.Let me introduce my set with the DSP!

1. power up squence( IO before core):1.8V->CVDD->CVDD1->1.5v->0.75V.->

2. Reset qpuence: RESETZ# de-assert ->POR# de_assert ->RESETFULL# de-assert

3.GPIO 1-13 : 1011100000110

my problem is that DSP always fail to boot from the SPI-Flash.I observe the waveform of spi_clk .There are about three phenomens as below:

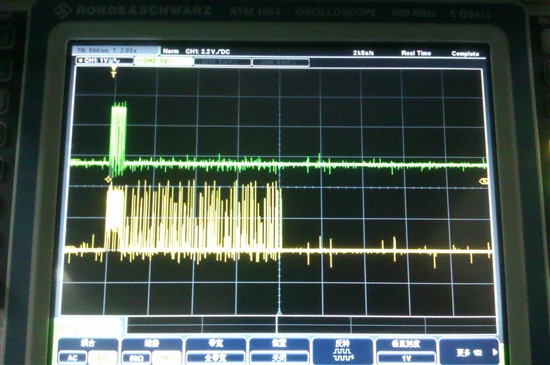

1.there is only a short time with the 500KHz clk.(seems to deliver the command data of DSP ).as shown picture below .( the blue is the uncorrect boot,the yellow is correct boot ,and we can see the freq of the clk which behind the 500KHz is 20MHz ,we exactly set the boot frequence at 20MHz. )

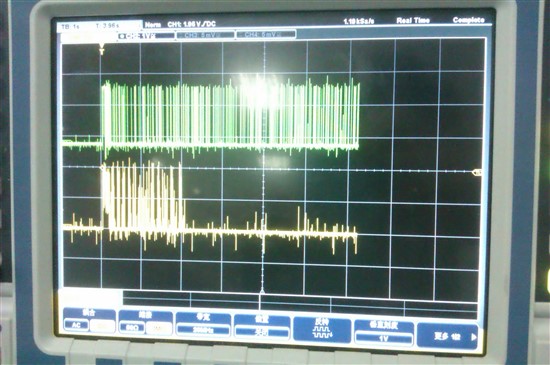

2.As picture below,there is too long time clk bebind the 500KHz.and its frequency is about 6.33MHz but not the 20mhz .Meanwhile the pin bootcomplete will pull high,but my DSP run uncorrectly with PLL unlocked.

(the blue is the uncorrect boot,the yellow is correct boot )

3. there is shorter 20MHz clk than the clk when it is boot correctly.link the DSP through JTAG,i found there is olnly core0 boot correctly,core1-7 don't boot at all .

I have checked all the thing as possible as i can, can you give me some advices.

Thank you very much !!!

Best regards!

Brian.