Hello,

In our setup we have an FPGA (Xilinx xc6lx16) and a NAND chip (MT29F2G16AADWP) connected to the EMIF bus. Our file system is located on the NAND chip, and the FPGA has a FIFO we want to retrieve data from via EMIF. When performing a DMA read transaction from the FIFO on the FPGA at the same time as data is being read from NAND we get ECC errors from the NAND reads:

“mtd->read(0x800 bytes from 0x60a0000) returned ECC error”

If instead of using DMAs to access the FIFO data we just use memory reads we never see this issue.

We’ve used the FPGA’s on chip analyzer to look at the EMIF bus during these transactions to see if that would give us any insight.

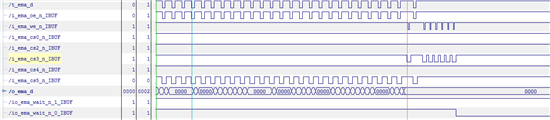

Below is a capture from the DMA scenario in which ECC errors are being reported by the file system. The FPGA is on Chip Select 5 (i_ema_cs5_n) and the NAND is on Chip Select 3 (i_ema_cs3_n). In this scenario it seems the NAND read request has been postponed by the DMA and there is a slight overlap in the last data word from the DMA and the beginning of a read request to NAND.

Below is a capture from the memory read scenario in which no ECC errors are reported. In this case the NAND read request in interlaced between FIFO reads, however, no errors occur.

Does anyone have any tips or insight into why the use of DMAs seem to be causing EMIF data corruption?

Thanks,

\Greg