Hi,

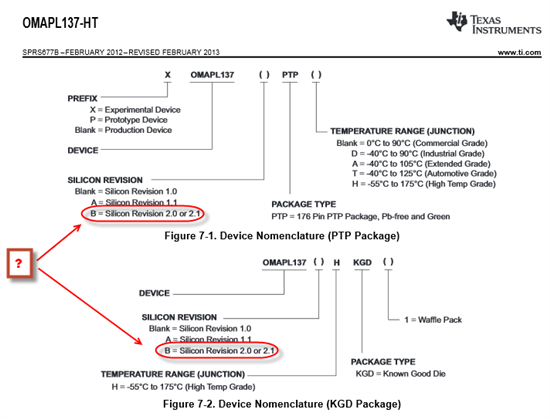

We are working with part # OMAPL137HTBPTPH-YF-1BA1TZW G4, in which the nomenclature on the Datasheet indicates that 'B' indicates silicon version 2.0 or 2.1, can it please be clarified what specific version that is so we can know if the Errata Advisory 2.0.20 is present or not?

This is urgent as we are in the final stages of the bootloader process and we are not sure if we are hitting this bug or not.

Thanks,

Miguel A. Alanis