Hi all:

I want to design a transcode(first decode then encode) system using some pieces of tci6638k2k.The target system firstly decode the input_1080p mpeg2 bitstream into the output_yuv data.Then the yuv data was devided into three ways and sent three different destinations.

The first way ,yuv data 1080p was encoded into 1080p H.264 bitstream.The second way,yuv data 1080p was scaled down to 720p and then encoded into 720p H.264 bitstream.The third way ,yuv data 1080p was scaled down to CIF 352x288 and then encoded into CIF H.264 bitstream.

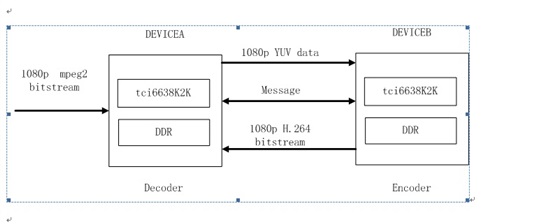

The figure describle the transcode system.In order to simplify I just paint one way 1080p mpeg2 decoded and H.264 encoded.

Device include one piece of tci6638k2k and DDR.

DeviceA is responsible for decoding.

DeviceB is responsible for encoding.

Message: used to communicate with each other.

Data Sequence:

1080p mpeg2 -> DeviceA -> 1080p YUV data -> DeviceB -> 1080p H.264

.