Hello, guys, I have a question about external LCD using DM8168 vout[0].

I connected VOUT[0]_R_CR[9]--VOUT[0]_R_CR[4] , VOUT[0]_G_Y_YC[9]--VOUT[0]_G_Y_YC[4] , VOUT[0]_B_CB_C[9]--VOUT[0]_B_CB_C[4] with 75LVDS84A transmitter to drive a 18bit LCD display.

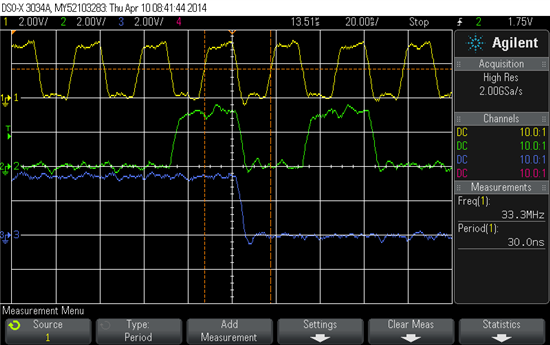

There are some green dots when the LCD displays some images, like follows:

Anyone could help me?

Thanks,