Hi,

I have one question regarding DDR3 signal of AM3874.

I would like to know how to terminate of DQ and DQS singal of AM3874.

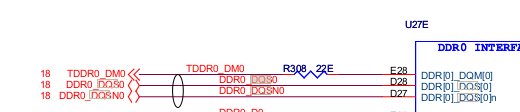

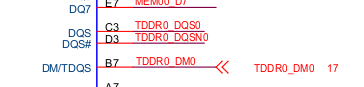

Is the above the schematic of I/O buffer for DQ and DQS correct? I would like to the position of I/O buffer and termination resistor.

Please let me know.

Best regards,

Michi