Dear Experts,

We meet rare case.

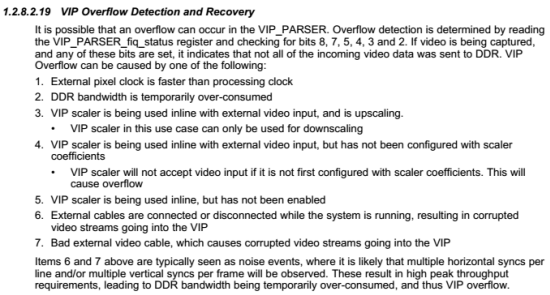

Sometimes we meet "Overflow detected on VIP0".

We use FPGA to calculate the signal CRC error when "Overflow detected on VIP0" happens, but there is no CRC error.

We try to execute heavy menory bandwidth loading to duplicate this issue, but still not happen.

Is there any method to identify to root cause of this issue?

Thx ~

HB

-

Ask a related question

What is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.