Hello,

I try connect a beaglebone revA5 to a FPGA, to do so I use the AM335x GPMC in 16b non mux synchronous NOR mode. On the oscilloscope Write access works, read access seems also OK, but on processor side I always read zeros. If I try with this in asynchronous mode it works except for the first read.

Here is my init code:

AM335X_REG(AM335X_CM_PER_GPMC_CLKCTRL) |= 2;

while((AM335X_REG(AM335X_CM_PER_GPMC_CLKCTRL) & 0x00030000) != 0 );

AM335X_REG(AM335X_GPMC_SYSCONFIG) |= 2;

while((AM335X_REG(AM335X_GPMC_SYSSTATUS) & 0x1) != 1 );

unsigned temp = AM335X_REG(AM335X_GPMC_SYSCONFIG);

temp &= !(3<<3);

temp |= 1<<3;

AM335X_REG(CONF_GPMC_CLK)|=1<<5;

AM335X_REG(AM335X_GPMC_SYSCONFIG) = temp;

AM335X_REG(AM335X_GPMC_IRQENABLE) = 0;

AM335X_REG(AM335X_GPMC_TIMEOUT_CONTROL) = 0 ;

AM335X_REG(AM335X_GPMC_CONFIG1_i(usedbank)) =

AM335X_GPMC_CONFIG1_READTYPE_SYNC |

AM335X_GPMC_CONFIG1_WRITETYPE_SYNC |

AM335X_GPMC_CONFIG1_CLKACTIVATIONTIME1 |

AM335X_GPMC_CONFIG1_DEVICESIZE_16b |

AM335X_GPMC_CONFIG1_DEVICETYPE_NOR |

AM335X_GPMC_CONFIG1_MUXADDDATA_NON_MUX |

AM335X_GPMC_CONFIG1_TIMEPARAGRANULARITY1 |

AM335X_GPMC_CONFIG1_GPMCFCLKDIVIDER0;

AM335X_REG(AM335X_GPMC_CONFIG2_i(usedbank)) =

AM335X_GPMC_CONFIG2_CSONTIME2 |

AM335X_GPMC_CONFIG2_CSWROFFTIME10 |

AM335X_GPMC_CONFIG2_CSRDOFFTIME10;

AM335X_REG(AM335X_GPMC_CONFIG3_i(usedbank)) =

AM335X_GPMC_CONFIG3_ADVONTIME2 |

AM335X_GPMC_CONFIG3_ADVWROFFTIME4 |

AM335X_GPMC_CONFIG3_ADVRDOFFTIME4;

AM335X_REG(AM335X_GPMC_CONFIG4_i(usedbank)) =

AM335X_GPMC_CONFIG4_OEONTIME6 |

AM335X_GPMC_CONFIG4_OEOFFTIME10 |

AM335X_GPMC_CONFIG4_WEONTIME6 |

AM335X_GPMC_CONFIG4_WEOFFTIME10 ;

AM335X_REG(AM335X_GPMC_CONFIG5_i(usedbank)) =

AM335X_GPMC_CONFIG5_RDCYCLETIME15 |

AM335X_GPMC_CONFIG5_WRCYCLETIME10 |

AM335X_GPMC_CONFIG5_RDACCESSTIME12 ;

AM335X_REG(AM335X_GPMC_CONFIG6_i(usedbank)) =

AM335X_GPMC_CONFIG6_CYCLE2CYCLEDELAY1 |

AM335X_GPMC_CONFIG6_WRDATAONADMUXBUS0 |

AM335X_GPMC_CONFIG6_WRACCESSTIME9 ;

AM335X_REG(AM335X_GPMC_CONFIG7_i(usedbank)) =

AM335X_GPMC_CONFIG7_MASKADDRESS_16M |

AM335X_GPMC_CONFIG7_CSVALID |9;

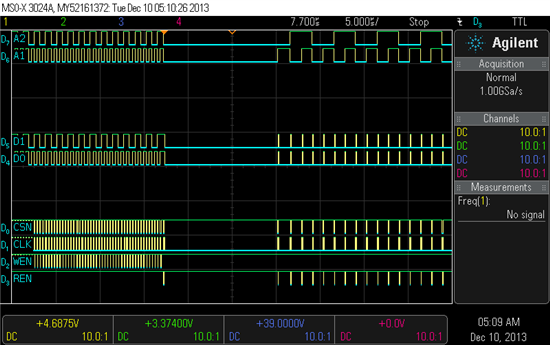

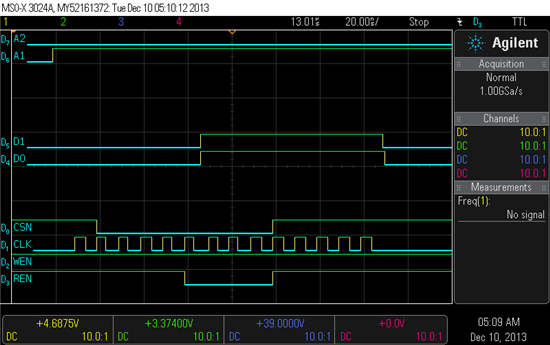

I attached some scope captures, there is a big delay between the first read and the second one is it normal?

On this one the Data stay high while I get clk but it's not due to the FPGA, the output enable is directly connected to an outbuff oen which is asynchronous.