Other Parts Discussed in Thread: AM3352

Hi folks,

Booting Linux on a custom board here. We're using the Micrel KSZ8081RNAIA phy, What I see is that the MDIO and PHY kernel modules load and are initialized, as you can see here in my kernel output:

[ 0.122924] BPF: phy_init: called

[ 0.122924] BPF: mdio_bus_init: mdio init

Also, after .9 seconds, we flip a GPIO to HIGH which pulls the PHY out of reset. Until this point, the PHY has been held in reset.

[ 0.913635] BPF: gpio1_init: Init of GPIO, RESET of RMII should go high here

Then after about 50ms more, we see the MDIO begin to poll the registers on all 32 PHY addresses looking for the right PHY IDs. Sadly, it seems to find all Fs instead:

[ 0.952301] BPF: get_phy_id: identifying phy...

[ 0.957061] BPF: mdiobus_read: Address being queried is 0, register 2

[ 0.963745] BPF: mdiobus_read: Address being queried is 0, register 3

[ 0.970428] phy ID: ffffffff

[ 0.973449] BPF: get_phy_device: Found PHY ID ffffffff

[ 0.978759] BPF: get_phy_device: Device was all Fs, nothing there, bail out

[ 0.985992] BPF: get_phy_id: identifying phy...

[ 0.990692] BPF: mdiobus_read: Address being queried is 1, register 2

[ 0.997375] BPF: mdiobus_read: Address being queried is 1, register 3

[ 1.004089] phy ID: ffffffff

[ 1.007049] BPF: get_phy_device: Found PHY ID ffffffff

[ 1.012390] BPF: get_phy_device: Device was all Fs, nothing there, bail out

(this continues through PHY address 31)

Then of course our Micrel PHY driver code fails, because none of the PHYs had the expected PHY IDs:

[ 2.032348] Fixed MDIO Bus: probed

[ 2.035888] BPF: ksphy_init: Invoking micrel driver code

[ 2.043182] BPF: ksphy_init: Did not find any devices matching our phy IDs

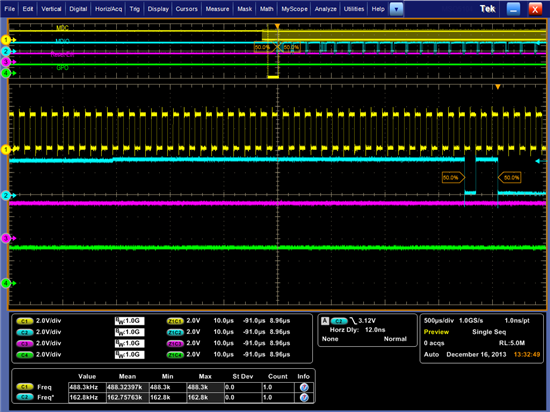

So our question is: What could make the MDIO unable to poll the PHY IDs from the PHY? We've verified that the reset lines are really high (where low means reset), so the chip should be out of reset. We've verified the pin-muxing for the MDIO/MDC, and are seeing traffic on it after Linux boots. We've also done some verification on the clocking and verified that the PHY clocks are working. We also are able to use the PHYs from U-boot, and the PHY ID is detected, and our pin muxing is the same there.