Other Parts Discussed in Thread: AM1810, PROFIBUS, ISO1176, FLASHTOOL, OMAP-L138, AM1808

Hi Everyone! We meet some problems that have bothered us for a long time. So I depict my problems here and really appreciate you can participate in this discussion. If you want any more details, please don't hesitate to post your comment here. Thank you in advance.

My team is using AM1810 Evaluation Module(+UART EXPANSION BOARD) on our windfarm simulation platform. But there are some problems we met for a long time which we cannot handle. Are you familiar with AM1810 (used for Profibus-DP)? and if yes, could you please help with it?

1. Our test conditions:

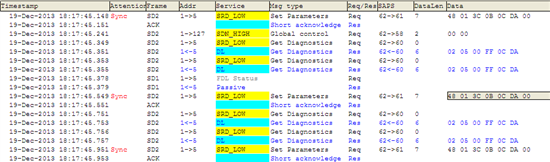

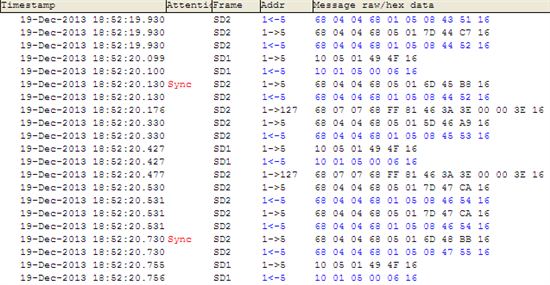

- Hardwares(①Mainboard: AM1810 Evaluation Module+UART EXPANSION BOARD;②DP analyser: ProfiTrace 2)

- Softwares (①AM1810-Linux 2.6.33.7-rt29; ②The program used for DP analyser is DPSlave_EVAL-am181x_profibus_dpslave_app-04.01.00.00; ③GSD:am181x_profibus_dpslave_app-04.01.00.00-PRU_0CDA.GSD)

2. When we use ProfiTrace as Profibus Master Station, AM1810 profibus EVM slave works normally at Baud rate of 6M(we test it by using 1byte). However, we cannot detect slave's existence at Baud rate of 12M (Shows station not exists). But AM1810 product specifcation says it can reach 12 M.

3. When we use CX1500-M310 from Beckhoff as profibus Master, and use TwinCAT to set AM 1810 profibus EVM as DP slave, cycle time=20ms, test it with 1 byte, and Baud rate 3M.

- when we have a stable input(only 1 byte) such as 0x06, Data Exchange shows normal.

- But when we have 1 byte input periodically changed, Data Exchange shows unstable and the real status as follows: 0-No error; 2-Station not exists; 8-Station not ready; 11-Physical faults. It keeps like these status.

Have you ever met this situation before? This has confused us for a long time. We will appreciate a lot if you can help us to figure out this problem. Thank you! I hope you also enjoy this technical discussion.

Comment from Mr. Thomas Mauer: "However, if you are facing instability issues with high baud rates, one root cause could be missing termination resistor(s) at the end of each line. The AM1810 EVM does not have termination resistors populated (as far as I know). Does your Profibus connector has the ability to add termination resistor? The one we have do have a small switch on the connector, which will enable or disable the termination inside the connector."

Reply to Thomas: We have a simple system-a master station and a slave station. And indeed we have termination resistors at both ends of master and slave.